تصنيع النبائط

| عمليات تصنيع أشباه الموصلات |

|---|

|

|

MOSFET scaling (process nodes) |

|

|

المستقبل

|

تصنيع النبائط أو تصنيع عناصر أشباه الموصلات إنگليزية: Semiconductor device fabrication هو العملية المستخدمة لتصنيع الأجهزة الشبه موصلة (النبائط)، وعادة ما تكون دوائر متكاملة (ICs) مثل معالجات الحواسيب والمتحكمات الدقيقة وشرائح الذاكرة (مثل ذاكرة فلاش NAND وDRAM) التي توجد في الأجهزة الكهربائية والإلكترونية اليومية. إنها عملية ليثوغرافية ضوئية (طباعة ضوئية) وفيزيو-كيميائية متعددة الخطوات (مثل التأكسد الحراري وترسيب الطبقة الرقيقة وزرع الأيونات والتنقيش) يتم خلالها إنشاء الدوائر الإلكترونية تدريجياً على رقاقة، والذي يتكون عادة من مادة شبه موصلة بلورية نقية واحدة. يتم استخدام السليكون دائماً، ولكن تستخدم مواد شبه موصلة مركبة مختلفة لتطبيقات متخصصة.

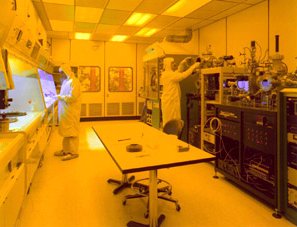

تتم عملية تصنيع النبائط في مصانع أشباه موصلات متخصصة للغاية، تسمى أيضاً بالمسابك أو "الفابات"[1]والجزء المركزي فيها هو "الغرفة النظيفة". في أجهزة الشبه الموصلات الأكثر تقدماً، مثل النقاط الحديثة بدقة 14/10/7 nm، يمكن أن تستغرق عملية التصنيع ما يصل إلى 15 أسبوعاً، مع متوسط صناعة يتراوح بين 11 إلى 13 أسبوعاً.[2] أما الإنتاج في مرافق التصنيع المتقدمة فهو مؤتمت بشكل كامل ويتم تنفيذه في بيئة محكمة مختومة بالنيتروجين لتحسين العائد (نسبة الشرائح الدقيقة التي تعمل بشكل صحيح في الرقاقة)، حيث تتولى أنظمة التحكم الآلي في التعامل مع المواد نقل الأقراص من آلة إلى أخرى. يتم نقل الأقراص داخل وحدات الحماية للقرص الدقيق (FOUPs)، وهي صناديق بلاستيكية مختومة خاصة. يحتوي جميع الآلات ووحدات FOUPs على جو داخلي من النيتروجين. يتم الحفاظ على نظافة داخل معدات التصنيع ووحدات FOUPs بشكل أفضل من الهواء المحيط في غرفة النظافة. يُعرف هذا الجو الداخلي بالبيئة الصغيرة.[3]تحتاج المصانع إلى كميات كبيرة من النيتروجين السائل للحفاظ على الجو داخل معدات الإنتاج ووحدات FOUPs، حيث يتم تطهيرها باستمرار باستخدام النيتروجين.[4]

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

حجم المنتجات

لعملية تصنيع النبائط قواعد محددة بشأن الحجم الأدنى (العرض أو CD) والتباعد للخصائص على كل طبقة من شريحة الدائرة المتكاملة. [5]عادةً ما تكون لدى عملية شبه موصلات جديدة أحجام أدنى أصغر وتباعد أضيق. في بعض الحالات، يتيح هذا تقليص بسيط للشريحة التي يتم إنتاجها حالياً لتقليل التكاليف وتحسين الأداء،[5] وزيادة كثافة الترانزستورات (عدد الترانزستورات في كل ملم مربع) دون تكلفة تصميم جديدة.

كانت لدى عمليات الشبه موصلات الأولى أسماء تجريبية للأجيال (مثل HMOS III، CHMOS V، أو COSMOS). في وقت لاحق، أصبحت تسمى كل عملية جيل جديد بمصطلح عقدة تكنولوجية أو عقدة[6] أو عقدة العملية،[7][8]والتي تحدد بحجم الخاصية الأدنى للعملية بالنانومتر (أو في الماضي بالميكرومترات) لطول بوابة الترانزستور للعملية، مثل "عملية "90 نانومتر". ومع ذلك، لم تعد هذه هي الحالة منذ عام 1994.[9] وأصبحت الأعداد المستخدمة في تسمية عقدات العملية بالنانومتر (انظر الخريطة الطريقية التكنولوجية الدولية للشبه موصلات) تُعتبر أكثر كونها مصطلح تسويقي ولا تتعلق بشكل موحد بأحجام الخصائص الوظيفية أو بكثافة المفاتيح (عدد المفاتيح في كل ملم مربع).[10]

في البداية، كان طول بوابة المفتاح النصفي أقل من الذي يوحي به اسم عقدة العملية (على سبيل المثال، عقدة 350 نانومتر)، ومع ذلك، عكس هذا الاتجاه في عام 2009.[9] على سبيل المثال، تتمتع عملية 10 نانومتر السابقة لشركة إنتل في الواقع بخصائص (أطراف الأعمدة في تقنية FinFET) بعرض 7 نانومتر، وبالتالي فإن عملية 10 نانومتر لشركة إنتل تشبه في كثافة المفاتيح عملية 7 نانومتر لشركة TSMC. أما عمليات 12 و14 نانومتر لشركة GlobalFoundries فلها أحجام خصائص مماثلة.[11][12][10]

تاريخ

القرن العشرون

تم تطوير تكنولوجيا سيموس المحسّنة لمفتاح موسفت من قبل تشيه-تانغ ساه وفرانك وانلاس في فيرتشايلد لأشباه الموصلات في عام 1963. [13][14] وقد سوِّقت من قبل RCA في أواخر الستينيات. [13] استخدمت RCA تجارياً تكنولوجيا CMOS للدوائر المتكاملة في سلسلة 4000 في عام 1968، بدءاً من عملية بعرض 20 ميكرومتر ثم تدريجياً تحجيمها إلى عملية بعرض 10 ميكرومتر خلال السنوات التالية.[15]

انتشر تصنيع النبائط من ولايتي تكساس وكاليفورنيا في الستينات إلى باقي أنحاء العالم، بما في ذلك آسيا وأوروبا والشرق الأوسط.

القرن الواحد والعشرون

أصبحت صناعة أشباه الموصلات اليوم عملاً عالمياً. وعادةً ما تمتلك الشركات المصنعة الرائدة للشرائح الإلكترونية مرافق في جميع أنحاء العالم. تعتبر شركة سامسونگ للإلكترونيات، أكبر مصنع للشرائح الإلكترونية في العالم، ولديها مرافق في كوريا الجنوبية والولايات المتحدة. وتعد إنتل، ثاني أكبر مصنع، لديه مرافق في أوروبا وآسيا بالإضافة إلى الولايات المتحدة. أما شركة تايوان لصناعة أشباه الموصلات، فهي أكبر مسبك تصنيع النبائط في العالم، ولديها مرافق في تايوان والصين وسنغافورة والولايات المتحدة. شركتي كوالكوم وبرودكم هما من أكبر شركات الشرائح الإلكترونية (تصنيع النبائط) التي لا تمتلك مصانع خاصة بها، بل تستعين بشركات مثل TSMC لإنتاج منتجاتهم.[16] ولديهما أيضاً مرافق موزعة في دول مختلفة.

منذ عام 2009، أصبحت "النود" اسماً تجارياً يُستخدم لأغراض التسويق للدلالة على أجيال جديدة من تقنيات العمليات، دون أي صلة بطول الخطوة أو المسافة بين المعادن أو المسافة بين البوابات. [17][18][19]على سبيل المثال، تقنية مسابك غلوبل بحجم 7 نانومتر مشابهة لتقنية إنتل بحجم 10 نانومتر، وبالتالي أصبح المفهوم التقليدي للعملية المستخدمة في تصنيع النبائط غير واضح.[20]بالإضافة إلى ذلك، تقنيات TSMC وسامسونج بحجم 10 نانومتر أكثر كثافة قليلاً من تقنية إنتل بحجم 14 نانومتر من حيث كثافة الترانزستورات. فهي في الواقع أقرب بكثير إلى تقنية إنتل بحجم 14 نانومتر منها إلى تقنية إنتل بحجم 10 نانومتر (على سبيل المثال، مسافة الشريط في تقنيات سامسونج بحجم 10 نانومتر هي نفس مسافة شريط تقنية إنتل بحجم 14 نانومتر: 42 نانومتر).[21][22]

بحلول عام 2019، كانت شرائح بحجم 14 نانومتر و10 نانومتر في عملية الإنتاج الضخم لدى إنتل، UMC، TSMC، سامسونج، ميكرون، إس كيه هاينكس، ذاكرة توشيبا وغلوبل للمسابك، مع بدء إنتاج شرائح بحجم 7 نانومتر بواسطة TSMC وسامسونج، على الرغم من أن تعريفهما للنود بحجم 7 نانومتر مشابه لعملية إنتل بحجم 10 نانومتر. بدأت سامسونج إنتاج شرائح بحجم 5 نانومتر في عام 2018. [23] وبحلول عام 2019، كانت تقنية النود بأعلى كثافة للترانزستور هي نود 5 نانومتر لدى TSMC.[24] بكثافة تبلغ 171.3 مليون ترانزستور في الملم المربع.[25]في عام 2019، أعلنت سامسونج وTSMC عن خطط لإنتاج نود بحجم 3 نانومتر. قررت غلوبل للمسابك التوقف عن تطوير نودات جديدة تزيد عن 12 نانومتر لتوفير الموارد، حيث توصلت إلى أن إنشاء وحدة تصنيع جديدة للتعامل مع طلبات أقل من 12 نانومتر ستتجاوز قدرات الشركة المالية.[26] اعتبارا من 2019[تحديث]، كانت سامسونج الرائدة في صناعة تقنيات تصغير الشرائح الإلكترونية المتقدمة، تليها TSMC ثم إنتل.[27]

قائمة الخطوات

هذه قائمة بتقنيات المعالجة التي يتم استخدامها عدة مرات خلال عملية بناء الأجهزة الإلكترونية الحديثة؛ هذه القائمة لا تعني بالضرورة ترتيباً محدداً، ولا يتم تطبيق جميع التقنيات خلال عملية التصنيع، حيث يكون الترتيب والتقنيات المستخدمة غالباً مرتبطة بعروض العمليات التي يقدمها المصانع أو الشركات المصنعة المتكاملة (IDM) لمنتجاتهم الخاصة، وقد لا تحتاج جهاز شبه موصل لجميع التقنيات. يتم تصنيع المعدات اللازمة لتنفيذ هذه العمليات من قبل عدد قليل من الشركات. يجب اختبار جميع المعدات قبل بدء مصنع تصنيع الشرائح الدقيقة.[28] يتم تنفيذ هذه العمليات بعد تصميم الدوائر المتكاملة.

- معالجة الرقائق

- تنظيف رطب

- تنظيف بواسطة المذيبات مثل الأسيتون، ثلاثي كلورو الإيثيلين والماء فائق النقاء.

- محلول البيرانا

- خطوات تنظيف RCA

- التخميل السحطي

- الطباعة الضوئية

- تغطية الفوتوريزيست (المقاومة للضوء) (غالباً كسائل، على القرص بأكمله)

- التحميص المقاوم للضوء (التصلب في الفرن)

- التعريض (في جهاز التصوير الضوئي بالخطوات، الماسح الضوئي أو قناع التقويم)

- عملية التطوير (إزالة أجزاء من المادة المضادة باستخدام مطور سائل، مما يترك فقط أجزاء من القرص مكشوفة لعمليات زراعة الأيونات، وترسيب الطبقات، والنقش، إلخ.)

- غرس الأيونات (حيث يتم زراعة عوامل إشابة في القرص مكونة مناطق بتوصيلية متزايدة أو متناقصة)

- التنميش (التصنيع الدقيق)

- الترسيب الكميائي للبخار (CVD)

- الترسيب الططبقي الذري (ALD)

- الترسيب الفيزيائي للبخار (PVD)

- نمو موجه للحزمة الجزيئية (MBE)

- تطهير البلازما (لإزالة المقاومة للضوء بالكامل، يتم تنفيذها تاريخياً باستخدام مذيب كيميائي، للسماح للأقراص بالمرور بجولة أخرى من تقنية الصور الضوئية)

- العلاجات الحرارية

- الانفصال بواسطة الليزر (لإنتاج الصمامات الثنائية المشعة LED)[29])

- الترسيب الكهربائي الكيميائي (ECD). انظر طلاء كهربائي

- الصقل الميكانيكي-الكيميائي (CMP)

- اختبار الرقاقة (حيث يتم التحقق من الأداء الكهربائي باستخدام معدات الاختبار الآلي، ويمكن أيضاً إجراء التصنيف و/أو التقليم بالليزر في هذه الخطوة)

- تنظيف رطب

- تحضير القوالب

- تصنيع الفتحة عبر السيليكون (للدوائر المتكاملة ثلاثية الأبعاد)

- تركيب رقاقة السليكون (تثبيت رقاقة السليكون على إطار معدني باستخدام شريط القطع)

- تلميع وطحن ظهر الرقاقة السليكونية[30] (يقلل من سمك الرقاقة لأجهزة رقيقة مثل البطاقة الذكية أو بطاقة PCMCIA أو تراص وربط الرقاقات، ويمكن أن يحدث ذلك أيضاً أثناء قطع الرقاقة، في عملية تعرف بـ"قطع قبل الطحن" أو "DBG")[31][32])

- ربط الرقاقات وتراصها (للدوائر المتكاملة ثلاثية الأبعاد وأجهزة نظم الميكروالكتروميكانيكية)

- تصنيع طبقة إعادة التوزيع (لحزم WLCSP)

- عملية ضرب الرقاقة (لحزمة الفليب شيب شبكة كرات مصفوفة BGA وحزمة WLCSP)

- قص الشرائح أو قطع الرقاقة

- تغليف الدوائر المتكاملة

- تركيب الرقاقة (يتم تركيب الرقاقة على إطار الأطراف باستخدام معجون موصل أو فيلم تركيب الرقاقة)[33][34])

- ربط الدوائر المتكاملة: ربط الأسلاك، الربط الحراري (الترموسونيك)، الرقاقة المقلوبة أو ربط التركيب الأوتوماتيكي بالشريط (TAB)

- تغليف الدوائر المتكاملة أو تركيب الموصل الحراري المتكامل (IHS)

- عملية القولبة (باستخدام مركب بلاستيكي خاص يحتوي على مسحوق زجاجي كحشوة للتحكم في التمدد الحراري)

- التعريض للحرارة

- الطلاء الكهربائي (Electroplating) تُغلّف أطراف النحاس في إطار الأطراف بالقصدير لتسهيل عملية اللحام

- الحفر بالليزر أو الطباعة بالشاشة الحريرية

- عملية القص والتشكيل (Trim and form) تفصل إطارات الأطراف عن بعضها البعض وتقوم بثني أطراف الإطار الأسلاكية لتتمكن من تركيبها على لوحة الدوائر المطبوعة.

- اختبار الدوائر المتكاملة

يمكن أيضاً إجراء خطوات إضافية مثل عملية النقش بالأسيتون (Wright etch).

الوقاية من التلوث والعيوب

عندما كانت أبعاد العناصر أكبر بكثير من حوالي 10 ميكرومترات، لم يكن نقاء الشبه الموصل مشكلة كبيرة مثلما هو عليه اليوم في تصنيع النبائط. مع تزايد التكامل في الأجهزة، يجب أن تصبح غرف النظيفة أكثر نظافة. في الوقت الحاضر، يتم ضغط مصانع تصنيع النبائط بالهواء المرشح لإزالة أصغر الجسيمات التي يمكن أن تستقر على رقائق السيليكون وتساهم في العيوب. تحتوي أسقف غرف تنظيف النبائط الشبه الموصلة على وحدات ترشيح مروحة (FFUs) في فترات منتظمة لاستبدال الهواء في الغرفة وتنقيته بشكل مستمر. قد تحتوي معدات رأس المال للشبه الموصل أيضاً على وحدات ترشيح مروحة خاصة بها. تساهم وحدات ترشيح المروحة (FFUs)، جنباً إلى جنب مع الأرضيات المرتفعة التي تحتوي على شبكات، في ضمان تدفق هوائي طبقي، لضمان أن الجسيمات تنزلق فوراً إلى الأرض ولا تبقى معلقة في الهواء بسبب التشويشات. يُشترط على العمال في مصنع تصنيع النبائط الشبه الموصلة ارتداء بدلات الغرفة النظيفة لحماية الأجهزة من التلوث البشري.[35] لمنع التأكسد وزيادة الإنتاجية، قد تحتوي وحدات تخزين الشبائك (FOUPs) ومعدات رأس المال للنبائط الشبه الموصلة على بيئة محكمة مختومة من النيتروجين النقي بمستوى تصنيف ISO الفئة 1 للغبار. تعزل FOUPs ووحدات SMIF النبائط عن الهواء في غرفة التنظيف، مما يزيد من الإنتاجية بسبب تقليل عدد العيوب التي تسببها جسيمات الغبار. علاوة على ذلك، يتم الحد من عدد الأشخاص في غرفة التنظيف قدر الإمكان لتسهيل الحفاظ على بيئة الغرفة النظيفة، حيث يساهم وجود الأشخاص، حتى عند ارتداء بدلات الغرفة النظيفة، في إطلاق كميات كبيرة من الجسيمات، خاصة أثناء المشي.[36][35][37]

الرقائق

تتكون الرقاقة النموذجية من سليكون شديد النقاء يُنمّى في صبات أحادية البلورة (بوال) أسطوانية بواسطة عملية تشوكرالسكي بقطر يصل إلى 300 مم (أقل بقليل من 12 بوصة). يتم ثم تقطيع هذه البوالات إلى رقائق بسمك حوالي 0.75 مم وتلميعها للحصول على سطح منتظم ومستوٍ للغاية.

المعالجة

في تصنيع النبائط الشبه الموصلة، تندرج الخطوات المختلفة للمعالجة في أربع فئات عامة: الترسيب، الإزالة، القولبة، وتعديل الخصائص الكهربائية.

- عملية الترسيب هي أي عملية تسمح بنمو أو تغطية المواد أو نقلها إلى الرقاقة. تتضمن التقنيات المتاحة الترسيب الفيزيائي للبخار (PVD)، الترسيب الكيميائي للبخار (CVD)، الترسيب الكهروكيميائي (ECD)، النمو الموجه للشعاع الجزيئي (MBE)، ومؤخراً ترسيب الطبقة الذرية (ALD) وغيرها. يمكن فهم الترسيب على أنه يشمل تكوين طبقة الأكسيد عن طريق التأكسد الحراري أو تقنية الأكسدة الموضعية للسليكون على وجه التحديد.

- عملية الإزالة هي أي عملية تقوم بإزالة المواد من الشبيكة؛ وتشمل أمثلة على ذلك عمليات النقش (سواء الرطبة أو الجافة) وتسوية الكيميائية-الميكانيكية (CMP).

- النمذجة هي عملية تشكيل أو تعديل المواد المرسبة، وتشار إليها عموماً بالتصوير الضوئي. على سبيل المثال، في التصوير الضوئي التقليدي، يتم تغطية الشبيكة بمادة كيميائية تسمى الفوتوريزيست (المقاوم للضوء)، ثم يقوم جهاز يسمى المقلد أو ستيبر بتركيز صورة قناع على الرقاقة باستخدام ضوء طول موجة قصير. يتم غسل المناطق المعرضة (المقاوم للضوء "الفعال") بواسطة محلول المطوِّر. بعد الإزالة أو غيرها من العمليات، يتم إزالة الفوتوريزيست المتبقي بواسطة عملية "جافة" بالبلازما أو بواسطة الكيمياء "الرطبة".[38]

- شمل تعديل الخصائص الكهربائية في الماضي تشويب مصادر ومصرّفات الترانزستورات والبوليسيليكون (بواسطة أفران الانتشار في البداية ولاحقاً بواسطة غرس الأيونات). تلي هذه العمليات عمليات تلدين في الأفران أو في الأجهزة المتقدمة يتم التلدين الحراري السريع (RTA) لتفعيل الشوائب. تمديد تعديل الخصائص الكهربائية يشمل الآن أيضاً تقليل ثابت العزل للمواد في low-κ insulators ذات القيمة المنخفضة للكهربائية عن طريق التعرض [[أشعة فوق بنفسجية

|للضوء فوق البنفسجي]] في معالجة الأشعة فوق البنفسجية (UVP). وعادة ما يتم تحقيق التعديل بواسطة التأكسد، والذي يمكن أن يتم لإنشاء واجهات شبه الموصل-عازل، مثل التأكسد الموضعي للسليكون (LOCOS) لتصنيع ترانزستور الأثر الحقلي للأكاسيد المعدنية لأشباه الموصلات. تحتوي الشرائح الحديثة على ما يصل إلى أحد عشر مستوى من المعادن أو أكثر يتم إنتاجها في أكثر من 300 خطوة معالجة متتالية أو أكثر.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

معالجة الجزء الأمامي (الأول) من خط تصنيع النبائط (FEOL)

تشير معالجة الجزء الأمامي (الأول) من خط تصنيع النبائط FEOL إلى تكوين ترانزيستورات مباشرة في السليكون. يتم تصميم الرقاقة الخام عن طريق نمو طبقة سيليكون فائقة النقاء خالية من العيوب من خلال النمو الموجه للبلورات. في أحدث أجهزة المنطق، قبل خطوة التنضيد بالسليكون، يتم تنفيذ طرق لتحسين أداء الترانزستورات التي ستُبنى. تشمل طريقة واحدة إجراء خطوة توتر تتم فيها إيداع سلالة من السيليكون مثل السيليكون-الجرمانيوم (SiGe). بمجرد إيداع السيليكون المنضد، تتمدد الشبكة البلورية إلى حد ما، مما يؤدي إلى تحسين حركية الإلكترونات. طريقة أخرى تُعرف بتقنية السيليكون على العازل تشمل إدخال طبقة عازلة بين الشبيكة الخام من السيليكون والطبقة الرقيقة التالية من السيليكون المنضد. تؤدي هذه الطريقة إلى إنشاء ترانزستورات بتأثيرات فرعية مخفضة.

أكسيد البوابة والغرس

يتبع تنضيد العازل البوابي (عادة ثاني أكسيد السليكون)، ونمذجة البوابة، ونمذجة مناطق المنبع والمصرف، وزرع أو انتشار الشوائب التي تتم بعدها للحصول على الخصائص الكهربائية المتكاملة المطلوبة. في أجهزة الذاكرة العشوائية الدينامية (DRAM)، يتم أيضاً تصنيع المكثفات التخزينية في هذا الوقت، وعادة ما يتم تكديسها فوق المتراشرة الوصول (قامت شركة الذاكرة العشوائية الدينامية Qimonda التي أصبحت غير فعالة حالياً بتنفيذ هذه المكثفات بواسطة قنوات تم نقشها بعمق في سطح السليكون).

معالجة الجزء الأخير من خط تصنيع النبائط (BEOL)

الطبقات المعدنية

بمجرد إنشاء النبائط المختلفة، يجب ربطها معاً لتشكيل الدوائر الكهربائية المطلوبة. يحدث ذلك في سلسلة من خطوات معالجة الشريحة التي تعرف الجزء الأخير من خط تصنيع النبائط (BEOL) (لا يجب الخلط بينها وبين الجزء الأخير لتصنيع الشرائح)، والذي يشير إلى مراحل التغليف والاختبار). تتضمن معالجة BEOL إنشاء أسلاك توصيل معدنية متصلة تعزلها طبقات العازل. كان المواد العازلة التقليدية هي شكل من أشكال SiO2 أو زجاج السيليكات، ولكن في الآونة الأخيرة يتم استخدام مواد جديدة ذات ثابت عزل منخفض (مثل أكسيد السيليكون الكربوني)، والتي عادة ما توفر ثوابت عزل حوالي 2.7 (بالمقارنة مع 3.82 SiO2)، على الرغم من أنه يتم تقديم مواد ذات ثوابت تصل إلى 2.2 لشركات تصنيع الشرائح. يمكن استخدام المواد ذات ثوابت عزل عالية (High-κ) أيضاً كعوازل.

الربط

تاريخياً، كانت أسلاك المعدن مصنوعة من الألومنيوم. في هذا النهج للتوصيلات (المعروف أحياناً بـ الألومنيوم المطروح)، يتم ترسيب أفلام بطانة من الألومنيوم أولاً، ثم يتم قولبتها ونقشها، مما يترك أسلاكاً منفصلة. يتم بعد ذلك ترسيب المادة العازلة فوق الأسلاك المكشوفة. تتصل الطبقات المعدنية المختلفة ببعضها البعض عن طريق نقش ثقوب (تسمى "فيا") في المادة العازلة ثم ترسيب التنغستن فيها باستخدام تقنية الترسيب الكيميائي للبخار باستخدام هكسافلوريد التنغستن؛ يمكن لهذا النهج أن يُستخدم لا يزال (وغالباً ما يُستخدم) في تصنيع العديد من شرائح الذاكرة مثل الذاكرة العشوائية الدينامية (DRAM)، لأن عدد مستويات التوصيل يمكن أن يكون صغيراً (لا يزيد عن أربعة مستويات).

في السنوات الأخيرة، مع زيادة عدد مستويات التوصيل في الدوائر المنطقية بشكل كبير بسبب العدد الكبير من الترانزستورات المتصلة في المعالجات الدقيقة الحديثة، أصبح تأخير التوقيت في التوصيلات مهمة جداً، مما دفع إلى تغيير مادة التوصيل (من الألومنيوم إلى طبقة التوصيل بالنحاس) وتغيير مادة العازل (من ثاني أكسيد السيليكون إلى العوازل ذات الثوابت المنخفضة الحديثة). تأتي هذه التحسينات الأداءية أيضاً بتكلفة منخفضة من خلال معالجة الداماسين، التي تقضي على خطوات المعالجة السابقة. مع زيادة عدد مستويات التوصيل، يتطلب تسطيح الطبقات السابقة لضمان سطح مستو قبل عملية التصوير الضوئي التالية. بدون ذلك، ستصبح المستويات غير مستقيمة بشكل متزايد، وتمتد خارج عمق التركيز الضوئي المتاح لعملية التصوير الضوئي، وبالتالي تعوق القدرة على التنميط. تعد تقنية الـ CMP (التسوية الكيميائية الميكانيكية) الطريقة الأساسية لتحقيق هذا التسوية، على الرغم من أن إزالة النقش الجاف لا تزال تستخدم في بعض الأحيان عندما لا يزيد عدد مستويات التوصيل عن ثلاثة مستويات. يستخدم التوصيل بالنحاس طبقة حاجز كهربائي موصلة لمنع انتشار النحاس إلى محيطه (التطعيم).

اختبار الرقاقة

زادت الطبيعة المتسلسلة لمعالجة الرقائق من الطلب على قياس الأبعاد بين مراحل المعالجة المختلفة. على سبيل المثال، يتم استخدام قياس الأغشية الرقيقة بناءً على تقنية الانكسار أو الانعكاس للتحكم بشكل دقيق على سمك أكسيد البوابة، وكذلك سمك الرقاقة الفوتوغرافية ومعامل الانكسار ومعامل الامتصاص المقاوم للضوء للطلاءات الأخرى. [39] يتم استخدام معدات قياس الرقاقة للتحقق من عدم تعرض الرقائق للتلف من المراحل السابقة للاختبار؛ إذا فشلت العديد من القوالب في نفس الرقاقة، يتم التخلص من الرقاقة بأكملها لتجنب تكاليف المعالجة اللاحقة. تم استخدام القياس الافتراضي للتنبؤ بخصائص الرقاقة بناءً على الأساليب الإحصائية دون إجراء القياس الفعلي ذاته.[1]

اختبار الجهاز

بمجرد الانتهاء من عملية الخط الأول، يتم تعريض أجهزة الشرائح النصف موصلة أو (النبائط) إلى مجموعة متنوعة من الاختبارات الكهربائية لتحديد ما إذا كانت تعمل بشكل صحيح. يشار إلى النسبة المئوية للأجهزة على الشريحة التي تعمل بشكل صحيح بأنها العائد أو الربح. عادةً ما يكون المصنعون سريين بشأن عوائدهم،[40]ولكن يمكن أن تكون منخفضة بنسبة 30٪ فقط، وهذا يعني أنه يعمل كما هو مقصود فقط 30٪ من الشرائح على الشريحة. يعد التباين في العملية أحد الأسباب المتعددة للعوائد المنخفضة. يتم إجراء الاختبارات لمنع وجود شرائح خاطئة تتم تجميعها في حزم مكلفة نسبياً.

غالباً ما يكون العائد مرتبطًا بحجم الجهاز (الشريحة)، ولكن ليس بالضرورة. على سبيل المثال، في ديسمبر 2019، أعلنت TSMC عن عائد متوسط يبلغ حوالي 80٪، مع ذروة العائد لكل شريحة تصل إلى أكثر من 90٪ لشرائح الاختبار بحجم 5 نانومتر وحجم شريحة يبلغ 17.92 mm2. انخفض العائد إلى 32.0٪ مع زيادة حجم الشريحة إلى 100 mm2.[41] يمكن ملاحظة عددة عيوب قاتلة أو ضرر جسيم على الشريحة، بغض النظر عن حجم الشريحة، بوصفه كثافة العيب (أو D0) للشريحة لكل وحدة مساحة، عادةً cm2.

يقوم المصنع باختبار الشرائح الموجودة على الرقائق باستخدام جهاز اختبار إلكتروني يضغط برؤوس صغيرة على الشريحة. يقوم الجهاز بوضع قطرة من الصباغة على كل شريحة معيبة. حالياً، يكون تمييز الشرائح السيئة بواسطة الصبغ الإلكتروني ممكناً إذا تم تسجيل بيانات اختبار الوافر (النتائج) في قاعدة بيانات مركزية على الحاسوب، وتم تصنيف الشرائح في "حاويات" افتراضية وفقاً لحدود الاختبار المحددة مثل الترددات/الساعات القصوى للعمل وعدد النوى العاملة (القابلة للعمل بشكل كامل) لكل شريحة، وما إلى ذلك. يمكن رسم بيانات التصنيف الناتجة، أو تسجيلها، على خريطة الرقاقة لتتبع عيوب التصنيع وتمييز الشرائح السيئة. يمكن أيضاً استخدام هذه الخريطة أثناء تجميع وتعبئة الرقاقة. يتيح التصنيف تمكين إعادة استخدام الشرائح التي ستكون غير قابلة للقبول في منتجات ذات مستويات أدنى، كما هو الحال في حالة وحدات معالجة الرسومات (GPUs) ووحدات المعالجة المركزية (CPUs)، مما يزيد من إنتاج الأجهزة بشكل كبير، خاصةً نظرًا لأن القليل جدًا من الشرائح تكون قابلة للعمل بشكل كامل (مثل وجود جميع النوى تعمل بشكل صحيح، على سبيل المثال). يمكن استخدام الصمامات الإلكترونية لفصل أجزاء الشرائح مثل النوى، إما لأنها لم تعمل كما هو مقصود خلال عملية التصنيف، أو كجزء من تقسيم السوق (استخدام نفس الشريحة للفئات المنخفضة والمتوسطة والعليا). قد تحتوي الشرائح على أجزاء احتياطية تسمح بتمرير الشريحة بالكامل في اختبارها حتى لو كانت تحتوي على عدة أجزاء غير قابلة للعمل.

تتم اختبار رقائق الشرائح مرة أخرى بعد التعبئة، حيث قد يكون هناك نقص في أسلاك الربط أو يمكن أن يتأثر الأداء التناظري بواسطة العبوة. يشار إلى هذا بـ "اختبار النهائي". قد يتم أيضاً تصوير رقائق الشرائح باستخدام الأشعة السينية.

عادةً ما يتقاضى المصنع رسوماً عن وقت الاختبار، وأسعارها تتراوح في حدود السنتات لكل ثانية. تختلف أوقات الاختبار من بضعة ميلي ثانية إلى ثانيتين، ويتم تحسين برامج الاختبار لتقليل وقت الاختبار. كما أنه يمكن أيضاً إجراء اختبار متعدد الشرائح (متعدد المواقع) لأن العديد من المختبرات تمتلك الموارد اللازمة لإجراء معظم أو جميع الاختبارات بتوازي وعلى عدة شرائح في آن واحد.

غالباً ما يتم تصميم الشرائح بميزات "قابلية الاختبار" مثل سلاسل الفحص أو "اختبار ذاتي مدمج" لتسريع الاختبار وتقليل تكاليف الاختبار. في بعض التصميمات التي تستخدم عمليات مصنعية تناظرية متخصصة، يتم استخدام الليزر لتشكيل الرقائق أثناء الاختبار، من أجل تحقيق توزيع دقيق لقيم المقاومة كما هو محدد في التصميم.

التصاميم الجيدة تحاول اختبار الزوايا الحرجة وإدارتها إحصائياً (أقصى حدود سلوك السيليكون الناجمة عن درجة حرارة التشغيل العالية مجتمعة مع أقصى حدود خطوات معالجة المصنع). تتكيف معظم التصاميم مع الزوايا بحد أدنى 64 زاوية.

إنتاجية الجهاز

إن نسبة الإنتاجية للجهاز أو نسبة الأقراص المعمول بها (Die Yield) هي عدد رقائق العمل أو الأقراص الصحية على الشريحة، وتعطى بالنسبة المئوية نظراً لأن عدد رقائق (Die per wafer, DPW) قد يختلف اعتماداً على حجم الرقائق وقطر الرقاقة. تتسبب تدهور الإنتاجية في تقليل الإنتاجية، والتي كانت في الماضي تسببها بشكل رئيسي جسيمات الغبار، ومع ذلك منذ عقد 1990، أصبح تدهور الإنتاجية يسببه بشكل رئيسي تباين العملية، والعملية نفسها والأدوات المستخدمة في تصنيع الرقائق، على الرغم من أن الغبار لا يزال يشكل مشكلة في العديد من المصانع القديمة. تزداد تأثير جسيمات الغبار على الإنتاجية مع تقليص حجم الميزات باستخدام العمليات الأحدث. لقد ساهمت التشغيل التلقائي واستخدام بيئات داخلية صغيرة داخل معدات الإنتاج مثل FOUPs وSMIFs في تقليل عدد العيوب الناجمة عن جسيمات الغبار. يجب الحفاظ على نسبة الإنتاجية للأجهزة عالية لتقليل سعر بيع الرقائق الصالحة للعمل، حيث يتعين على الرقائق الصالحة للعمل أن تدفع ثمن الرقائق التي فشلت، ولتقليل تكلفة معالجة الوافر. يمكن أن تتأثر الإنتاجية أيضاً بتصميم وتشغيل المصنع.

من الضروري ممارسة رقابة صارمة على الملوثات وعملية الإنتاج لزيادة الإنتاجية. يمكن أن تكون الملوثات ملوثات كيميائية أو جسيمات غبار. "العيوب القاتلة" هي تلك التي تسببها جسيمات الغبار وتؤدي إلى فشل كامل للجهاز (مثل الترانزستور). هناك أيضاً عيوب بريئة. يجب أن يكون حجم الجسيم 1/5 حجم الميزة ليتسبب في عيب قاتل. لذا، إذا كانت الميزة تبلغ 100 نانومتر عرضاً، يجب أن يكون حجم الجسيم 20 نانومتر فقط ليتسبب في عيب قاتل. الكهرباء الساكنة أيضاً يمكن أن تؤثر سلباً على الإنتاجية. تشمل الملوثات الكيميائية أو الشوائب المعادن الثقيلة مثل الحديد والنحاس والنيكل والزنك والكروم والذهب والزئبق والفضة، والمعادن القلوية مثل الصوديوم والبوتاسيوم والليثيوم، وعناصر مثل الألومنيوم والمغنيسيوم والكالسيوم والكلور والكبريت والكربون والفلور. من المهم ألا تبقى هذه العناصر في اتصال مع السيليكون، حيث يمكن أن تقلل من الإنتاجية. يمكن استخدام خلائط كيميائية لإزالة هذه العناصر من السيليكون؛ وتكون الخلائط المختلفة فعالة ضد العناصر المختلفة.

تُستخدم عدة نماذج لتقدير الإنتاجية. تشمل هذه النماذج نموذج ميرفي ونموذج بواسون ونموذج الثنائي ونموذج مور ونموذج سيدز. لا يوجد نموذج عالمي؛ يجب اختيار النموذج استناداً إلى توزيع الإنتاجية الفعلي (موقع الرقائق المعيبة). على سبيل المثال، يفترض نموذج ميرفي أن فقد الإنتاجية يحدث بشكل أكبر على حواف القرص (حيث تتركز الرقائق غير العاملة على حواف القرص)، ويفترض نموذج بواسون أن الرقائق المعيبة موزعة بشكل متساوٍ نسبياً على القرص، ويفترض نموذج سيدز أن الرقائق المعيبة متجمعة معاً.[42]

تكلفة إنتاج الرقائق الأصغر تكون أقل (نظراً لإمكانية وضع المزيد من الرقائق على القرص، ويتم معالجة وتسعير القرص ككل)، ويمكن أن تساعد في تحقيق إنتاجية أعلى نظراً لأن الرقائق الأصغر لديها فرصة أقل لوجود عيب، نظراً لمساحتها الأقل على القرص. ومع ذلك، تتطلب الرقائق الأصغر حجماً أصغر لتحقيق نفس وظائف الرقائق الأكبر أو تفوقها، ويتطلب الحجم الأصغر تقليل التباين في العملية وزيادة النقاء (تقليل التلوث) للحفاظ على إنتاجية عالية. تُستخدم أدوات القياس لتفقد القرص خلال عملية الإنتاج وتوقع الإنتاجية، لذا يمكن تجاهل القرص المتوقع أن يحتوي على العديد من العيوب لتوفير تكاليف المعالجة.[40]

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

تحضير الرقائق

بعد إجراء الاختبارات، يتم عادة تقليل سمك الرقاقة في عملية تعرف أيضاً باسم "التخفيف الخلفي"،[43] "التشطيب الخلفي" أو "تنحيف القرص"[44] قبل أن يتم تسجيل الرقاقة ومن ثم كسره إلى رقائق فردية في عملية تعرف بتجزئة الرقاقة. يتم تعبئة فقط الرقائق الجيدة والغير مميزة.

التعبئة

تتضمن عملية تعبئة الرقائق بالبلاستيك أو السيراميك تثبيت الرقاقة وربط أطراف الرقاقة بالأطراف على العبوة وإغلاق الرقاقة. يتم استخدام أسلاك الربط الصغيرة لربط الأطراف بالأطراف. في "الأيام القديمة" (في السبعينيات)، كانت تلك الأسلاك توضع يدوياً، ولكن الآن تقوم الآلات المتخصصة بأداء هذه المهمة. في السابق، كانت تلك الأسلاك مصنوعة من الذهب، مما يؤدي إلى إطار من الرصاص المطلي باللحام؛ ونظراً لسمية الرصاص، فإن الآن يتم اشتراط إطارات "خالية من الرصاص" بموجب توجيهات RoHS.

العبوة بحجم الرقاقة (CSP) هي تكنولوجيا تعبئة أخرى. فعبوة ثنائية الأسلاك من البلاستيك، مثل معظم العبوات، أكبر بمرات عديدة من الرقاقة الفعلية المخبأة بداخلها، بينما تكون رقائق CSP تقريباً بحجم الرقاقة؛ يمكن بناء CSP لكل رقاقة قبل قطع الشريحة إلى رقائق منفصلة.

يتم إعادة اختبار الرقائق المعبأة للتأكد من عدم تعرضها للتلف أثناء التعبئة وتأكيد أن عملية ربط الرقاقة بالأسلاك تمت بشكل صحيح. يقوم ليزر بنقش اسم الرقاقة والأرقام على العبوة.

المواد الخطرة

يتم استخدام العديد من المواد السامة في عملية التصنيع.[45]ويتضمن ذلك:

- عناصر الإشابة السامة، مثل الزرنيخ والأنتيمون والفوسفور.

- مركبات سامة، مثل الأرسين، الفوسفين، هكسافلوريد التنغستن والسيلان.

- سوائل عالية النشاط التفاعلي، مثل بيروكسيد الهيدروجين، حمض النيتريك، حمض الكبريتيك، وحمض الهيدروفلوريك.

من الضروري ألا يتعرض العمال مباشرة لهذه المواد الخطرة. يساعد الدرجة العالية من الأتمتة المشتركة في صناعة تصنيع الدوائر المتكاملة على تقليل مخاطر التعرض. تستخدم معظم منشآت التصنيع أنظمة إدارة العوادم، مثل أجهزة تنقية المياه والمحرقات وحاويات الامتصاص المُسخنة، إلخ.، للسيطرة على مخاطر التي يتعرض لها العمال والبيئة.

جدول زمني لأنظمة الموسفتات المشتركة

انظر أيضاً

- Deathnium

- Glossary of microelectronics manufacturing terms

- قائمة أمثلة على مستوى النبائط

- موسفت

- Multigate device

- صناعة أشباه الموصلات

- International Technology Roadmap for Semiconductors

- Semiconductor consolidation

- أكسدة موضعية للسيليكون (LOCOS)

- List of integrated circuit manufacturers

- List of semiconductor fabrication plants

- تصنيع دقيق

- Semiconductor Equipment and Materials International (SEMI) —الرابطة التجارية لتصنيع النبائط

- SEMI font لوضع التسميات على الرقائق

- Etch pit density

- التخميل

- عملية سطحية

- عدد الترانزستورات

المراجع

- ^ أ ب Neurotechnology Group, Berlin Institute of Technology, IEEE Xplore Digital Library. “Regression Methods for Virtual Metrology of Layer Thickness in Chemical Vapor Deposition Archived 2020-02-25 at the Wayback Machine.” January 17, 2014. Retrieved November 9, 2015.

- ^ "8 Things You Should Know About Water & Semiconductors". China Water Risk (in الإنجليزية الأمريكية). 11 July 2013. Retrieved 2023-01-21.

- ^ Kure, Tokuo; Hanaoka, Hideo; Sugiura, Takumi; Nakagawa, Shinya (2007). "Clean-room Technologies for the Mini-environment Age" (PDF). Hitachi Review. 56 (3): 70–74. CiteSeerX 10.1.1.493.1460. S2CID 30883737. Archived (PDF) from the original on 2021-11-01. Retrieved 2021-11-01.

- ^ "FOUP Purge System - Fabmatics: Semiconductor Manufacturing Automation". www.fabmatics.com. Archived from the original on 2020-08-06. Retrieved 2020-01-04.

- ^ أ ب Shirriff, Ken (June 2020). "Die shrink: How Intel scaled-down the 8086 processor". Retrieved 22 May 2022.

- ^ "Overall Roadmap Technology Characteristics" (PDF). Semiconductor Industry Association.

- ^ Shukla, Priyank. "A Brief History of Process Node Evolution". Design And Reuse.

- ^ "Technology Node - WikiChip". Archived from the original on 2020-11-12. Retrieved 2020-10-20.

- ^ أ ب Moore, Samuel K. (21 July 2020). "A Better Way To Measure Progress in Semiconductors". IEEE Spectrum: Technology, Engineering, and Science News. Retrieved 22 May 2022.

- ^ أ ب Ridley, Jacob (April 29, 2020). "Intel 10nm isn't bigger than AMD 7nm, you're just measuring wrong". PC Gamer. Archived from the original on October 28, 2020. Retrieved October 21, 2020.

- ^ Cutress, Ian. "Intel's 10nm Cannon Lake and Core i3-8121U Deep Dive Review". www.anandtech.com. Archived from the original on 2020-11-12. Retrieved 2020-11-07.

- ^ "VLSI 2018: GlobalFoundries 12nm Leading-Performance, 12LP". 22 July 2018. Archived from the original on 7 April 2019. Retrieved 20 October 2020.

- ^ أ ب "1963: Complementary MOS Circuit Configuration is Invented". Computer History Museum. Archived from the original on 23 July 2019. Retrieved 6 July 2019.

- ^ Sah, Chih-Tang; Wanlass, Frank (February 1963). "Nanowatt logic using field-effect metal-oxide semiconductor triodes". 1963 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. VI: 32–33. doi:10.1109/ISSCC.1963.1157450.

- ^ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. p. 330. ISBN 9783540342588. Archived from the original on 2020-08-06. Retrieved 2019-07-21.

- ^ "Top 10 Worldwide Semiconductor Sales Leaders - Q1 2017 - AnySilicon". AnySilicon (in الإنجليزية الأمريكية). 2017-05-09. Archived from the original on 2017-11-06. Retrieved 2017-11-19.

- ^ Shukla, Priyank. "A Brief History of Process Node Evolution". design-reuse.com. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ Hruska, Joel (23 June 2014). "14nm, 7nm, 5nm: How low can CMOS go? It depends if you ask the engineers or the economists…". ExtremeTech. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ "Exclusive: Is Intel Really Starting To Lose Its Process Lead? 7nm Node Slated For Release in 2022". wccftech.com. 2016-09-10. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ "Life at 10nm. (Or is it 7nm?) And 3nm - Views on Advanced Silicon Platforms". eejournal.com. 2018-03-12. Archived from the original on 2019-07-09. Retrieved 2019-07-09.

- ^ "10 nm lithography process - WikiChip". en.wikichip.org. Archived from the original on 2019-07-01. Retrieved 2019-08-17.

- ^ "14 nm lithography process - WikiChip". en.wikichip.org. Archived from the original on 2019-07-01. Retrieved 2019-08-17.

- ^ Shilov, Anton. "Samsung Completes Development of 5nm EUV Process Technology". AnandTech. Archived from the original on 2019-04-20. Retrieved 2019-05-31.

- ^ Cheng, Godfrey (14 August 2019). "Moore's Law is not Dead". TSMC Blog. TSMC. Archived from the original on 16 August 2019. Retrieved 18 August 2019.

- ^ Schor, David (2019-04-06). "TSMC Starts 5-Nanometer Risk Production". WikiChip Fuse (in الإنجليزية الأمريكية). Archived from the original on 2020-05-05. Retrieved 2019-04-07.

- ^ Cutress, Anton Shilov, Ian. "GlobalFoundries Stops All 7nm Development: Opts To Focus on Specialized Processes". www.anandtech.com. Archived from the original on 2019-10-12. Retrieved 2019-10-12.

{{cite web}}: CS1 maint: multiple names: authors list (link) - ^ "Intel is "two to three years behind Samsung" in the race to 1nm silicon". PCGamesN. 20 May 2019. Archived from the original on 11 December 2019. Retrieved 11 December 2019.

- ^ "Power outage partially halts Toshiba Memory's chip plant". Reuters. June 21, 2019. Archived from the original on December 16, 2019. Retrieved December 16, 2019 – via www.reuters.com.

- ^ "Laser Lift-Off(LLO) Ideal for high brightness vertical LED manufacturing - Press Release - DISCO Corporation". www.disco.co.jp. Archived from the original on 2019-06-14. Retrieved 2019-05-26.

- ^ "Product Information | Polishers - DISCO Corporation". www.disco.co.jp. Archived from the original on 2019-05-26. Retrieved 2019-05-26.

- ^ "Product Information | DBG / Package Singulation - DISCO Corporation". www.disco.co.jp. Archived from the original on 2019-05-16. Retrieved 2019-05-26.

- ^ "Plasma Dicing (Dice Before Grind) | Orbotech". www.orbotech.com.[dead link]

- ^ "Electro Conductive Die Attach Film(Under Development) | Nitto". www.nitto.com. Archived from the original on 2019-05-26. Retrieved 2019-05-26.

- ^ "Die Attach Film Adhesives". www.henkel-adhesives.com. Archived from the original on 2019-05-26. Retrieved 2019-05-26.

- ^ أ ب "Study into human particle shedding". www.cleanroomtechnology.com. Archived from the original on 2020-10-15. Retrieved 2020-10-14.

- ^ "The ASYST SMIF system - Integrated with the Tencor Surfscan 7200". Chip History. Archived from the original on 2020-10-16. Retrieved 2020-10-14.

- ^ "How a Chip Gets Made: Visiting GlobalFoundries". PCMag Asia. February 15, 2018. Archived from the original on October 14, 2020. Retrieved October 14, 2020.

- ^ "Wafer Cleaning Procedures; Photoresist or Resist Stripping; Removal of Films and Particulates". www.eesemi.com. Archived from the original on 2020-10-15. Retrieved 2020-10-14.

- ^ Löper, Philipp; Stuckelberger, Michael; Niesen, Bjoern; Werner, Jérémie; Filipič, Miha; Moon, Soo-Jin; Yum, Jun-Ho; Topič, Marko; De Wolf, Stefaan; Ballif, Christophe (2015). "Complex Refractive Index Spectra of CH3NH3PbI3 Perovskite Thin Films Determined by Spectroscopic Ellipsometry and Spectrophotometry". The Journal of Physical Chemistry Letters. 6 (1): 66–71. doi:10.1021/jz502471h. PMID 26263093. Retrieved 2021-11-16.

- ^ أ ب "Yield and Yield Management" (PDF). Cost Effective Integrated Circuit Manufacturing (PDF). Integrated Circuit Engineering Corporation. 1997. ISBN 1-877750-60-3. Retrieved 2023-01-22.

- ^ Cutress, Dr Ian. "Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020". www.anandtech.com. Archived from the original on 2020-05-25. Retrieved 2020-04-12.

- ^ "Advanced MOSFETs and Novel Devices" (PDF). Archived from the original (PDF) on 2020-10-02. Retrieved 2020-10-23.

{{cite web}}:|archive-date=/|archive-url=timestamp mismatch; 2020-10-26 suggested (help) - ^ "Introduction to Semiconductor Technology" (PDF). STMicroelectronics. p. 6. Archived (PDF) from the original on 2018-04-03. Retrieved 2018-09-25.

- ^ "Wafer Backgrind". eesemi.com. Archived from the original on 2021-01-22. Retrieved 2020-12-18.

- ^ CNET. “Why tech pollution's going global Archived 2021-01-23 at the Wayback Machine.” April 25, 2002. Retrieved November 9, 2015.

للاستزادة

- Kaeslin, Hubert (2008), Digital Integrated Circuit Design, from VLSI Architectures to CMOS Fabrication, Cambridge University Press, section 14.2.

- Wiki related to Chip Technology

وصلات خارجية

- CS1 الإنجليزية الأمريكية-language sources (en-us)

- Articles with dead external links from January 2022

- CS1 errors: archive-url

- Short description matches Wikidata

- Articles containing إنگليزية-language text

- Articles with hatnote templates targeting a nonexistent page

- مقالات فيها عبارات متقادمة منذ 2019

- جميع المقالات التي فيها عبارات متقادمة

- تصنيع النبائط

- تقنية الغرفة النظيفة

- موسفت