دائرة مدمجة ثلاثية الأبعاد

الدائرة المدمجة ثلاثية الأبعاد three-dimensional integrated circuit (3D IC) هي عبارة عن MOS (أنصاف النواقل من أكاسيد المعادن) فهي الدوائر المتكاملة (IC) مصنعة من خلال تكديس رقائق السيليكون أو dies وتوصيلها للاستخدام الرأسي ، على سبيل المثال ، through-silicon via (TSVs) أو اتصالات Cu-Cu ، فهي تعمل كجهاز واحد لتحقيق تحسينات في الأداء في طاقة مخفضة وبصمة أصغر من العمليات التقليدية ثنائية الأبعاد. يعد 3D IC واحدًا من عدة مخططات متكاملة ثلاثية الأبعاد تستغل الاتجاه z لتحقيق فوائد الأداء الكهربائي ، في الإلكترونيات الدقيقة و الإلكترونيات النانوية.

يمكن تصنيف الدوائر المتكاملة ثلاثية الأبعاد حسب مستوى التسلسل الهرمي للترابط على المستوى (الحزمة) عالمياً ، المستوى المتوسط (اللوحة الرابطة) والمستوى المحلي (الترانزستور)[1] بشكل عام ، يعد التكامل ثلاثي الأبعاد مصطلحًا واسعًا يتضمن تقنيات مثل التغليف على مستوى رقاقة ثلاثية الأبعاد (3DWLP) ؛ 2.5D و 3D التكامل القائم على المتدخل. ICs ثلاثية الأبعاد (3D-SICs) ، ICs المتجانسة ثلاثية الأبعاد ؛ التكامل غير المتجانس 3D. وتكامل النظم ثلاثية الأبعاد.[2][3]

المنظمات الدولية مثل Jisso Technology Roadmap Committee عملت (JIC) و خارطة طريق التكنولوجيا الدولية لأنصاف النواقل (ITRS) على تصنيف مختلف تقنيات التكامل ثلاثي الأبعاد لتعزيز وضع المعايير وخرائط الطريق للتكامل ثلاثي الأبعاد.[4] اعتبارًا من 2010s ، تُستخدم 3D ICs على نطاق واسع لـ NAND ذاكرة الفلاش في الأجهزة المحمولة.

أنواع

3D ICs vs. 3D packaging

يشير التغليف ثلاثي الأبعاد إلى مخططات التكامل ثلاثية الأبعاد التي تعتمد على الطرق التقليدية للتوصيل مثل الربط السلكي و شريحة الانقلاب لتحقيق مكدسات رأسية. يمكن نشر التغليف ثلاثي الأبعاد في 3D نظام في الحزمة (3D SiP) و 3D حزمة مستوى الرقاقة (3D WLP) ، الذاكرة المكدسة المترابطة die مع روابط سلكية ، و حزمة على الحزمة ( تكوينات PoP) المرتبطة إما بالسندات السلكية ، أو رقائق الانقلاب عبارة عن SiPs ثلاثية الأبعاد التي كانت تعمل في التصنيع الرئيسي لبعض الوقت ولديها بنية تحتية راسخة. يستخدم PoP لدمج التقنيات المتباينة رأسياً مثل 3D WLP الذي يستخدم عمليات مستوى الرقاقة مثل طبقة إعادة التوزيع (RDL) وعمليات ارتطام الرقاقات لتشكيل الوصلات البينية.

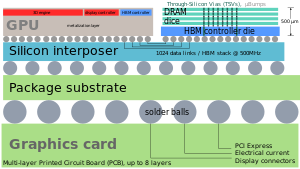

2.5D interposer هو أيضًا WLP ثلاثي الأبعاد يربط بين الجانب الآخر من السيليكون أو الزجاج أو المتداخل العضوي باستخدام TSVs و RDL. في جميع أنواع التغليف ثلاثي الأبعاد ، تتواصل الرقاقات الموجودة في الحزمة باستخدام إشارات خارج الرقاقة ، كما لو كانت مثبتة في حزم منفصلة على لوحة دوائر عادية.

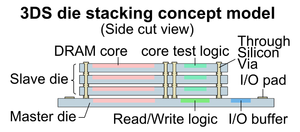

3D ICs يمكن تقسيمها إلى ICs ثلاثية الأبعاد (3D SIC) ، والتي تشير إلى تكديس رقائق IC باستخدام روابط TSV ، و ICs ثلاثية الأبعاد متجانسة ، والتي تستخدم تصنيعات الرقاقات لتحقيق روابط ثلاثية الأبعاد على المستويات المحلية للتسلسل الهرمي الأسلاك على الرقاقة كما هو موضح بواسطة في ITRS ، ينتج عن هذا روابط مباشرة رأسية بين طبقات الجهاز. تُلاحظ الأمثلة الأولى للنهج المتجانس في أجهزة سامسونگ ثلاثية الأبعاد V-NAND.[5]

اعتبارًا من 2010s ، تُستخدم حزم 3D ICs على نطاق واسع للذاكرة NAND flash في الأجهزة المحمولة.[6]

3D SiCs

يتطلب سوق الإلكترونيات الرقمية شريحة أعلى ذاكرة أنصاف النواقل لتلبية احتياجات مكونات CPU التي تم إصدارها مؤخرًا ، وقد تم اقتراح تقنية تكديس القوالب المتعددة كحل لهذه المشكلة. كشفت JEDEC أن تقنية DRAM القادمة تتضمن خطة التراص die"3D SiC" في "Server Memory Forum" ، 1-2 نوفمبر 2011 ، سانتا كلارا ، كاليفورنيا. في أغسطس 2014 ، فقد بدأت سامسونگ للإلكترونيات في إنتاج 64 GB SDRAM للخوادم بناءً على ذاكرة DDR4 (معدل بيانات مزدوج 4) الناشئة باستخدام تقنية حزمة TSV ثلاثية الأبعاد.[7] تتضمن المعايير المقترحة الجديدة للذاكرة الديناميكية ثلاثية الأبعاد المتراكمة ثلاثية الأبعاد I/O عريض ، I/O 2 عريض ، Hybrid Memory Cube ، ذاكرة النطاق الترددي العالي.

3D ICs المتجانسة

يتم دمج الدوائر المتكاملة المتجانسة ثلاثية الأبعاد في طبقات على رقاقة أنصاف نواقل واحدة ، والتي يتم التقطيع إلى مكعبات إلى 3D ICs. هناك ركيزة واحدة فقط ، وبالتالي لا حاجة للمحاذاة، أو التخفيف ، أو الترابط ، أو عبر وصلات بينية سيليكونية . يتم معالجة قيود درجة حرارة العملية بتقسيم تصنيع الترانزستور إلى مرحلتين. مرحلة درجة حرارة عالية تتم قبل نقل الطبقة يتبعها نقل طبقة باستخدام ion-cut, يُعرف أيضًا باسم نقل الطبقة ، والذي تم استخدامه لإنتاج رقائق سيليكون على عازل (SOI) على مدى العقدين الماضيين. يمكن إنشاء طبقات رفيعة متعددة (مقياس من 10 إلى 100 نانومتر) من السيليكون الخالي من الشوائب تقريبًا من خلال استخدام تقنيات ربط وشق ذات درجة حرارة منخفضة (<400 ℃) ، ووضعها فوق دوائر ترانزستور نشطة. يتبع ذلك بوضع اللمسات الأخيرة على الترانزستورات باستخدام عمليات الحفر والترسيب. تم بحث تقنية 3D IC المتجانسة هذه في جامعة ستانفورد بموجب منحة برعاية DARPA .

تقوم CEA-Leti أيضًا بتطوير مناهج 3D IC ، تسمى 3D IC متسلسلة. في عام 2014 ، قدم معهد الأبحاث الفرنسي CoolCube ™ ، وهو تدفق عملية منخفض الحرارة يوفر مسارًا حقيقيًا لـ 3DVLSI.[8] في جامعة ستانفورد ، يقوم الباحثون بتصميم 3D IC باستخدام هياكل الأنابيب النانوية الكربونية (CNT) مقابل السيليكون باستخدام عمليات نقل CNT ذات درجة الحرارة المنخفضة على نطاق الرقاقة والتي يمكن إجراؤها عند 120 ℃.[9]

بشكل عام ، لا تزال 3D IC المتجانسة تقنية متطورة ويعتبرها معظمهم بعيدًا عن الإنتاج بعدة سنوات.

تقنيات التصنيع لـ 3D SiCs

هناك العديد من الطرق لتصميم 3D IC ، بما في ذلك إعادة التبلور وطرق ربط رقاقة. هناك نوعان رئيسيان من ربط الرقاقة ، توصيلات Cu-Cu (توصيلات النحاس بالنحاس)[10]و عبر وصلات السيليكون البينية (TSV). اعتبارًا من عام 2014 ، تم إطلاق عدد من منتجات الذاكرة مثل ذاكرة النطاق الترددي العالي (HBM) و Hybrid Memory Cube التي تعمل على تكديس 3D IC مع TSVs. هناك عدد من مناهج التراص الرئيسية التي يتم تنفيذها واستكشافها. وتشمل هذه die-to-die, die-to-wafer, و wafer-to-wafer.

- Die-to-Die

- المكونات الإلكترونية مبنية على قوالب متعددة ، يتم بعد ذلك عمل محاذاة وربطها. يمكن عمل ترقيق و TSV قبل أو بعد الترابط. ميزة واحدة من die-to-die هو أن كل قالب die يمكن اختباره أولاً ، بحيث لا يؤدي قالب واحد سيئ إلى إتلاف مجموعة كاملة.[11] علاوة على ذلك ، يمكن أن يتم تجميع كل قالب في 3D IC مسبقًا ، بحيث يمكن مزجها ومطابقتها لتحسين استهلاك الطاقة والأداء (على سبيل المثال ، مطابقة المكعبات المتعددة من زاوية نعالجة الطاقة المنخفضة لتطبيقات الهاتف المحمول).

- Die-to-Wafer

- المكونات الإلكترونية مبنية على رقاقة من أنصاف النواقل . مكعبات رقاقة واحدة. يتم عمل محاذاة للمكعب وربطها في مواقع قوالب الرقاقة الثانية. كما هو الحال في طريقة رقاقة على رقاقة ، يتم إجراء عملية الترقيق وإنشاء TSV إما قبل أو بعد الترابط. يمكن إضافة قالب إضافي إلى المكدسات قبل التكعيب.

- Wafer-to-Wafer

- المكونات الإلكترونية مبنية على اثنين أو أكثر من رقائق أنصاف النواقل ، والتي يتم محاذاتها بعد ذلك ، وربطها ، و تكعيبها إلى دوائر ثلاثية الأبعاد. يمكن تخفيف كل رقاقة قبل أو بعد الترابط. التوصيلات العمودية إما مدمجة في الرقائق قبل الترابط أو يتم إنشاؤها في المكدس بعد الربط. هذه "من خلال وصلات السيليكون البينية" (TSVs) تمر عبر ركيزة (طبقات) السيليكون بين الطبقات النشطة و / أو بين الطبقة النشطة و ركيزة حزمة خارجية. يمكن أن يقلل الترابط من الرقاقة إلى الرقاقة من الإنتاجية ، نظرًا لأنه إذا حوت أي من رقائق "N" في 3D IC خللاً ما ، فسيكون 3D IC معيبًا. علاوة على ذلك ، يجب أن تكون الرقائق بنفس الحجم ، ولكن يتم تصنيع العديد من المواد الغريبة (مثل III-Vs) على رقائق أصغر بكثير من CMOS logic أو DRAM (عادةً 300 مم) ، مما يعقد التكامل غير المتجانس.

فوائد

في حين تعمل عمليات CMOS التقليدية على تحسين سرعة انتشار الإشارة ، أصبح التوسع من تقنيات التصنيع الحالية وتصميم الرقائق أكثر صعوبة وتكلفة ، ويرجع ذلك جزئيًا إلى قيود كثافة الطاقة ، وجزئيًا لأن الروابط لا تصبح أسرع أثناء عمل الترانزستورات .تعالج 3D IC [12]تحدي التوسع من خلال تكديس قوالب ثنائية الأبعاد وربطها في البعد الثالث. هذا يعد بتسريع الاتصال بين رقائق الطبقات ، مقارنة بالتخطيط المستوي.[13] وعدت 3D ICs بالعديد من الفوائد الهامة ، بما في ذلك:

- البصمة

- هذا ما يناسب المزيد من وظائف المساحة الصغيرة. وهذا ما يمتد إلى قانون مور ويفعّل جيلًا جديدًا من الأجهزة الصغيرة والقوية.

- التكلفة

- يمكن أن يؤدي تقسيم شريحة كبيرة إلى عدة قوالب أصغر مع التراص ثلاثي الأبعاد إلى تحسين العائد وتقليل تكلفة التصنيع إذا تم اختبار القوالب الفردية بشكل منفصل.[14][15]

- التكامل الغير متجانس

- يمكن بناء طبقات الدائرة مع عمليات مختلفة ، أو حتى على أنواع مختلفة من الرقائق. هذا يعني أنه يمكن تحسين المكونات إلى درجة أكبر بكثير مما لو تم بناؤها معًا على رقاقة واحدة. علاوة على ذلك ، يمكن دمج المكونات ذات التصنيع غير المتوافق في 3D IC واحد.[16][3]

- اتصال أقصر

- يتم تقليل متوسط طول السلك. فالأرقام الشائعة التي أبلغ عنها الباحثون تتراوح بين 10-15 ٪ ، لكن هذا الانخفاض ينطبق في الغالب على التوصيل البيني الأطول ، والذي قد يؤثر على تأخير الدائرة بمقدار أكبر. بالنظر إلى أن الأسلاك ثلاثية الأبعاد لها سعة أعلى بكثير من الأسلاك التقليدية ، فإن تأخير الدائرة قد يتحسن أو لا يتحسن.

- الطاقة

- يمكن أن يؤدي الاحتفاظ بإشارة على الشريحة إلى تقليل استهلاك الطاقة بمقدار 10-100 مرة.[17]تقلل الأسلاك القصيرة أيضًا من استهلاك الطاقة من خلال إنتاج السعة الطفيلية أقل.[18]يؤدي تقليل ميزانية الطاقة إلى تقليل توليد الحرارة وإطالة عمر البطارية وانخفاض تكلفة التشغيل.

- التصميم

- يضيف البعد الرأسي ترتيبًا أعلى للاتصال ويوفر إمكانات تصميم جديدة.[3]

- أمن الدائرة

- يمكن تحقيق التكامل ثلاثي الأبعاد الأمن من خلال الضبابية ؛ يعقد الهيكل المكدس محاولات الهندسة العكسية للدائرة. يمكن تقسيم الدوائر الحساسة أيضًا بين الطبقات بطريقة تحجب وظيفة كل طبقة.[19] علاوة على ذلك ، يسمح التكامل ثلاثي الأبعاد بدمج ميزات مخصصة لمراقب النظام في طبقات منفصلة.[3] الهدف هنا هو تنفيذ نوع من أجهزة جدار الحماية لرصد أي مكونات / شرائح سلعة في وقت التشغيل ، سعياً لحماية النظام الإلكتروني بأكمله من هجمات وقت التشغيل أيضًا كتعديلات للأجهزة الضارة.

- عرض النطاق الترددي

- يسمح التكامل ثلاثي الأبعاد بأعداد كبيرة من الفتحات الرأسية بين الطبقات. يسمح هذا ببناء نواقل ذات عرض نطاق عريض بين الكتل الوظيفية في طبقات مختلفة. من الأمثلة النموذجية على ذلك معالج + مكدس الذاكرة ثلاثي الأبعاد ، مع تكديس ذاكرة التخزين المؤقت أعلى المعالج. يسمح هذا الترتيب بوجود ناقل أوسع بكثير من 128 بت أو 256 بت بين ذاكرة التخزين المؤقت والمعالج.[20] تعمل النواقل الواسعة بدورها على تخفيف مشكلة جدار الذاكرة.[21]

تحديات

ولأن هذه التكنولوجيا جديدة فإنها تحمل تحديات جديدة ، بما في ذلك:

- التكلفة

- على الرغم من أن التكلفة تعتبر فائدة عند مقارنتها بالتدرج ، فقد تم تحديدها أيضًا على أنها تحدٍ أمام التسويق التجاري 3D ICs في تطبيقات المستهلك السائدة. ومع ذلك ، يجري العمل على معالجة هذا. على الرغم من أن تقنية 3D جديدة ومعقدة إلى حد ما ، إلا أن تكلفة عملية التصنيع تكون مباشرة بشكل مدهش عند تقسيمها إلى الأنشطة التي تبني العملية بأكملها. من خلال تحليل مجموعة الأنشطة التي تكمن أساساً ، يمكن تحديد عوامل التكلفة. بمجرد تحديد عوامل التكلفة ، يصبح الأمر أقل تعقيدًا لتحديد مصدر معظم التكلفة ، والأهم من ذلك ، أين يمكن تخفيض التكلفة.[22]

- العائد

- فكل خطوة تصنيع إضافية تضيف خطرًا للعيوب. لكي تكون الدوائر المتكاملة ثلاثية الأبعاد قابلة للتطبيق تجاريًا ، يمكن إصلاح العيوب أو تحملها ، أو يمكن تحسين كثافة العيوب.[23][24]

- الحرارة

- يجب تبديد الحرارة المتراكمة داخل المكدس. هذه مسألة حتمية لأن التقريب الكهربائي يرتبط بالتقريب الحراري. يجب إدارة النقاط الساخنة الحرارية المحددة بعناية أكبر.

- تعقيد التصميم

- تتطلب الاستفادة الكاملة من التكامل ثلاثي الأبعاد تقنيات تصميم معقدة وأدوات جديدة CAD.[25]

- النفقات العامة المقدمة من TSV

- تكون TSV كبيرة مقارنةً بالبوابات ومخططات الأرضيات . عند العقدة ذات التكنولوجيا 45 نانومتر ، فإن مساحة المنطقة لـ 10μm x 10μm TSV يمكن مقارنتها مع حوالي 50 بوابة.[26]علاوة على ذلك ، تتطلب قابلية التصنيع ركائز هابطة ومناطق محمية مما يزيد من مساحة منطقة TSV. اعتمادًا على خيارات التكنولوجيا ، تحظر TSVs مجموعة فرعية من موارد التخطيط.[26]يتم تصنيع TSVs Via-first قبل المعدنة ، وبالتالي تشغل طبقة الجهاز وتؤدي إلى عوائق في الموضع. يتم تصنيع TSVs Via-last بعد المعدنة ويمر عبر الشريحة. وبالتالي ، فإنها تشغل كل من الجهاز والطبقات المعدنية ، مما يؤدي إلى عوائق في التموضع والتوجيه. بينما من المتوقع بشكل عام أن يقلل استخدام TSVs طول السلك ، هذا يعتمد على عدد TSVs وخصائصها.[26] أيضا ، فإن دقة تجزئة التقسيم بين الأجزاء تؤثر على طول السلك. عادةً ما ينخفض هذا النوع من التفاصيل الدقيقة (الكتل ذات الوحدات 20-100) و الخشنة (التقسيم على مستوى الكتلة) ، ولكن يزيد من الدقة (التقسيم على مستوى البوابة).[26]

- الاختبار

- لتحقيق عائد إجمالي مرتفع وخفض التكاليف ، من الضروري إجراء اختبار منفصل لقوالب مستقلة.[24][27] ومع ذلك ، فإن التكامل الضيق بين الطبقات النشطة المتجاورة في 3D ICs يستلزم قدرًا كبيرًا من الترابط بين الأقسام المختلفة من نفس وحدة الدائرة التي تم تقسيمها إلى قوالب مختلفة. بصرف النظر عن النفقات العامة الهائلة التي قدمتها TSVs المطلوبة ، فإن أقسام هذه الوحدة ، على سبيل المثال ، المضاعف ، لا يمكن اختباره بشكل مستقل من خلال التقنيات التقليدية. ينطبق هذا بشكل خاص على المسارات الحرجة للتوقيت الواردة في الأبعاد الثلاثية....

- نقص المعايير

- هناك عدد قليل من المعايير لتصميم وتصنيع وتغليف 3D IC القائم على TSV ، على الرغم من معالجة هذه المشكلة.[28][29] بالإضافة إلى ذلك ، هناك العديد من خيارات التكامل التي يتم استكشافها مثل via-last, via-first, via-middle;[30] المتوسطات[31] أو حزم مباشرة إلخ.

- سلسلة تزويد التكامل غير المتجانسة

- في الأنظمة المتكاملة غير المتجانسة ، فإن تأخير جزء واحد من أحد موردي الأجزاء المختلفة يؤخر تسليم المنتج بأكمله ، وبالتالي يؤخر الإيرادات لكل من موردي الأجزاء 3D IC .

- عدم وجود ملكية محددة بوضوح

- من غير الواضح من يجب أن يمتلك تكامل 3D IC والتعبئة / التجميع. يمكن أن تكون أماكن التجميع مثل ASE أو المنتج OEM.

أساليب التصميم

اعتمادًا على تقسيم التفاصيل ، يمكن تمييز أنماط التصميم المختلفة. يواجه التكامل على مستوى البوابة تحديات متعددة ويبدو حاليًا أقل عملياً من التكامل على مستوى الكتلة.[32]

- تكامل على مستوى البوابة

- هذا النمط يقسم الخلايا القياسية بين قوالب متعددة. فقد تعهد بتقليل طول السلك و إضافة مرونة كبيرة. ومع ذلك ، يمكن تقليل تخفيض طول الأسلاك ما لم يتم الحفاظ على وحدات ذات حجم أدنى معين. من ناحية أخرى ، تشمل آثاره السلبية العدد الهائل من TSVs اللازمة للربط البيني. يتطلب نمط التصميم هذا أدوات ثلاثية الأبعاد place-and-route ، وهي غير متاحة حتى الآن. أيضًا ، يعني تقسيم كتلة التصميم عبر قوالب متعددة أنه لا يمكن أن يكون الاختبار كاملاً قبل تكديس القوالب. بعد تكديس القالب (اختبار post-bond ) ، يمكن أن يؤدي القالب الفاشل الواحد إلى جعل العديد من القوالب الجيدة غير قابلة للاستخدام ، مما يقوض و يقلل من الإنتاجية. يضاعف هذا النمط أيضًا تأثير اختلاف العملية ، وخاصة اختلاف inter-die. في الواقع ، قد ينتج عن التخطيط ثلاثي الأبعاد بشكل سيئ أكثر من نفس الدائرة الموضوعة في ثنائي الأبعاد ، على عكس التعهد الأصلي بتكامل 3D IC.[33] علاوة على ذلك ، يتطلب نمط التصميم هذا إعادة تصميم الملكية الفكرية المتاحة ، نظرًا لأن IP الحالية وأدوات EDA لا تنص على التكامل ثلاثي الأبعاد.

- تكامل على مستوى الكتلة

- يعين هذا النمط كتل تصميم كاملة لقوالب منفصلة. تستهلك كتل التصميم معظم اتصال netlist وترتبط بعدد صغير من الترابطات الشاملة. لذلك ، يعد التكامل على مستوى الكتلة بتخفيض النفقات العامة على TSV. تتطلب الأنظمة ثلاثية الأبعاد المتطورة التي تجمع بين القوالب غير المتجانسة عمليات تصنيع متميزة في عقد تقنية مختلفة لمنطق عشوائي سريع ومنخفض الطاقة ، وأنواع عديدة من الذاكرة ، ودوائر تناظرية وترددات لاسلكية ، وما إلى ذلك. يبدو التكامل على مستوى الكتلة ، والذي يسمح بعمليات تصنيع منفصلة ومحسنة ، أمرًا بالغ الأهمية للتكامل ثلاثي الأبعاد. علاوة على ذلك ، قد يسهل هذا النمط الانتقال من التصميم الثنائي الأبعاد الحالي إلى تصميم 3D IC. بشكل أساسي ، هناك حاجة إلى أدوات حساسة ثلاثية الأبعاد فقط للتقسيم والتحليل الحراري.[34] سيتم تصميم قوالب منفصلة باستخدام أدوات ثنائية الأبعاد (معدلة) وكتل ثنائية الأبعاد. الدافع وراء ذلك هو التوافر الواسع لمجموعات IP الموثوقة. من الملائم أكثر استخدام كتل IP ثنائية الأبعاد المتاحة ووضع TSVs الإلزامية في المساحة غير المشغولة بين الكتل بدلاً من إعادة تصميم كتل IP وتضمين TSVs.[32] تعتبر هياكل التصميم للاختبار مكونًا رئيسيًا في مجموعات IP ، وبالتالي يمكن استخدامها لتسهيل اختبار الدوائر المتكاملة ثلاثية الأبعاد. أيضًا ، يمكن تضمين المسارات الحرجة في الغالب داخل كتل ثنائية الأبعاد ، مما يحد من تأثير TSV واختلاف inter-die على إنتاجية التصنيع. أخيرًا ، يتطلب التصميم الحديث للرقاقة غالبًا تغييرات هندسية في اللحظة الأخيرة. إن تقييد تأثير مثل هذه التغييرات على القوالب الفردية أمر أساسي للحد من التكلفة.

تاريخ

بعد عدة سنوات من اقتراح دائرة MOS المتكاملة (MOS IC) لأول مرة بواسطة محمد عطا الله في مختبرات Bell في عام 1960,[35]فقد تم اقتراح مفهوم الدائرة المتكاملة ثلاثية الأبعاد MOS من قبل الباحثين تكساس إنسترومنتس روبرت دبليو هايستي ، رولاند إي جونسون وإدوارد دبليو ميهال في عام 1964.[36] و في عام 1969 ، اقترح باحثو NEC كاتسوهيرو أونودا ، وريو إيگاراشي ، وتوشيو وادا ، وشو ناكانوما ، وتورو تسوجيد ، مفهوم الدائرة المتكاملة ثلاثية الأبعاد MOS رقاقة الذاكرة..[37]

3D ICs التجارية(2004 – للوقت الحالي)

كان أول استخدام تجاري معروف لشريحة IC ثلاثية الأبعاد في Sony PlayStation Portable (PSP) وحدة تحكم الألعاب المحمولة ، الذي تم إصداره في عام 2004. أجهزة PSP تتضمن eDRAM (مضمن DRAM) ذاكرة تم تصنيعها بواسطة Toshiba في شريحة النظام داخل الحزمة ثلاثية الأبعاد مع شريحتين قوالب مكدسة رأسياً.[6]فقد أطلقت عليها توشيبا اسم "ذاكرة DRAM شبه مدمجة" في ذلك الوقت ، قبل أن تطلق عليها لاحقًا مكدس " chip-on-chip" (CoC).[6][38]

في أبريل 2007 ، قامت شركة توشيبا بتسويق شريحة 3D IC من ثماني طبقات ، وهي شريحة ذاكرة 16 GB THGAM متضمنة NAND flash ، والتي تم تصنيعها بثمانية شرائح مكدسة 2 GB كرقائق فلاش NAND.[39] في سبتمبر 2007 ، قدمت Hynix تقنية 3D IC من 24 طبقة ، مع شريحة ذاكرة فلاش 16 GB تم تصنيعها باستخدام 24 شريحة NAND مكدسة باستخدام عملية ربط الرقاقة.[40]استخدمت شركة Toshiba أيضًا 3D IC لرقاقة فلاش THGBM بسعة 32 GB في عام 2008.[41] في عام 2010 ، استخدمت توشيبا تقنية 3D IC مكونة من 16 طبقة لشريحة فلاش 128 GB ، والتي تم تصنيعها ب16 رقاقة مكدسة 8 GB.[42] في عام 2010 ، دخلت 3D IC في الاستخدام التجاري على نطاق واسع في شكل حزمة متعددة الرقائق و حزمة على حزمة كحلول للذاكرة NAND flash في الأجهزة المحمولة.[6]

طورت Elpida Memory أول رقاقة 8 GB DRAM (مكدسة مع أربعة DDR3 SDRAM dies) في سبتمبر 2009 ، وأصدرتها في يونيو 2011.[43]أعلنت TSMC خطط لإنتاج 3D IC مع تقنية TSV في يناير 2010.[43] في عام 2011 ، قدمت SK Hynix فئة 16 16 GB DDR3 SDRAM (40 nm class) باستخدام تقنية TSV,[44] و قدمت Samsung Electronics مكدسًا ثلاثي الأبعاد 32 GB DDR3 (30 nm class) based on TSV in في سبتمبر ، و أعلنت شركة Samsung و Micron Technology عن تقنية Hybrid Memory Cube (HMC) المعتمدة على TSV في أكتوبر.[43]

ذاكرة النطاق الترددي العالي (HBM) ، التي طورتها Samsung ، AMD و SK Hynix ، تستخدم رقائق مكدسة و TSVs. تم تصنيع أول شريحة ذاكرة HBM بواسطة SK Hynix في عام 2013.[44] في كانون الثاني (يناير) 2016 ، أعلنت Samsung Electronics عن الإنتاج الضخم المبكر لـ HBM2 ، بما يصل إلى 8 GB لكل حزمة.[45][46]

في عام 2017 ، قامت Samsung Electronics بدمج تكديس 3D IC مع تقنية V-NAND ثلاثية الأبعاد (استنادًا إلى تقنية flash trap flash) ، وتصنيع رقاقة ذاكرة فلاش 512 GB KLUFG8R1EM f بسعة ثمانية مكدسات 64 طبقة V-NAND كرقائق.[47] في عام 2019 ، أنتجت Samsung شريحة فلاش 1 TB مع 16 قالب V-NAND مكدس.[48][49] اعتبارًا من 2018 ، بدأت Intel بالأخذ بعين الاعتبار في استخدام 3D ICs لتحسين الأداء.[50] اعتبارًا من أبريل 2019 ، حصلنا على أجهزة الذاكرة ذات شرائح 96 طبقة التي يمكن شراؤها من أكثر من مصنع. و أيضاً توشيبا بعد أن صنعت أجهزة 96 طبقة في 2018.

انظر أيضاً

- Charge trap flash (CTF)

- FinFET (3D transistor)

- MOSFET

- Multigate device (MuGFET)

- V-NAND (3D NAND)

ملاحظات

- ^ "SEMI.ORG" (PDF). Archived (PDF) from the original on 2015-09-24.

- ^ "What is 3D Integration? - 3D InCites". Archived from the original on 2014-12-30.

- ^ أ ب ت ث J. Knechtel, O. Sinanoglu, I. M. Elfadel, J. Lienig, C. C. N. Sze, "Large-Scale 3D Chips: Challenges and Solutions for Design Automation, Testing, and Trustworthy Integration" Archived 2017-08-07 at the Wayback Machine, in IPSJ Transactions on System LSI Design Methodology, vol. 10, pp. 45–62, Aug. 2017

- ^ "INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2011 EDITION" (PDF). Archived from the original (PDF) on 2014-12-30. Retrieved 2014-12-30.

- ^ "Comparing Samsung's 3D NAND with Traditional 3D ICs". 2013-08-16.

- ^ أ ب ت ث James, Dick (2014). "3D ICs in the real world". 25th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC 2014): 113–119. doi:10.1109/ASMC.2014.6846988. ISBN 978-1-4799-3944-2.

- ^ "Samsung starts production of 3D DDR4 DRAM modules". 2014-08-27. Archived from the original on 2014-12-31.

- ^ Michallet, Jean-Eric. "CoolCube™: A True 3DVLSI Alternative to Scaling". www.3DInCites.com. Archived from the original on January 22, 2016. Retrieved March 24, 2014.

- ^ von Trapp, Francoise (2015-03-16). "Monolithic 3D IC Heats Up at DATE 2015". 3D InCites. 3D InCites. Archived from the original on April 2, 2015. Retrieved March 16, 2015.

- ^ Reif, Rafael; Tan, Chuan Seng; Fan, Andy; Chen, Kuan-Neng; Das, Shamik; Checka, Nisha (2002). "3-D Interconnects Using Cu Wafer Bonding: Technology and Applications" (PDF). Advanced Metallization Conference: 37–44. Retrieved 15 July 2019.

- ^ Real World Technologies. "3D Integration: A Revolution in Design". May 2, 2007. "3D Integration: A Revolution in Design". Archived from the original on 2010-12-22. Retrieved 2011-03-18.

- ^ Developer, Shed. "3D Processors, Stacking Core". September 20, 2005. "Archived copy". Archived from the original on 2012-03-16. Retrieved 2012-10-29.

{{cite web}}: CS1 maint: archived copy as title (link), - ^ Developer, Shed. "3D Processors, Stacking Core". September 20, 2005. "Archived copy". Archived from the original on 2011-07-09. Retrieved 2011-02-24.

{{cite web}}: CS1 maint: archived copy as title (link) - ^ Xiangyu Dong and Yuan Xie, "System-level Cost Analysis and Design Exploration for 3D ICs", Proc. of Asia and South Pacific Design Automation Conference, 2009, "Archived copy". Archived from the original on 2010-04-24. Retrieved 2010-05-20.

{{cite web}}: CS1 maint: archived copy as title (link) - ^ "3D IC Technology Delivers The Total Package" "Archived copy". Archived from the original on 2010-10-31. Retrieved 2011-01-27.

{{cite web}}: CS1 maint: archived copy as title (link) Electronic Design July 02, 2010 - ^ James J-Q Lu, Ken Rose, & Susan Vitkavage "3D Integration: Why, What, Who, When?" "Archived copy". Archived from the original on 2008-02-12. Retrieved 2008-01-22.

{{cite web}}: CS1 maint: archived copy as title (link) Future Fab Intl. Volume 23, 2007 - ^ William J. Dally, "Future Directions for On-Chip Interconnection Networks" page 17, "Archived copy" (PDF). Archived (PDF) from the original on 2010-06-12. Retrieved 2008-01-22.

{{cite web}}: CS1 maint: archived copy as title (link) Computer Systems Laboratory Stanford University, 2006 - ^ Johnson, R Colin. "3-D chip stacks standardized". July 10, 2008. "Archived copy". Archived from the original on 2012-09-30. Retrieved 2014-05-15.

{{cite web}}: CS1 maint: archived copy as title (link) - ^ "3D-ICs and Integrated Circuit Security" "Archived copy" (PDF). Archived (PDF) from the original on 2008-09-07. Retrieved 2008-02-08.

{{cite web}}: CS1 maint: archived copy as title (link) Tezzaron Semiconductor, 2008 - ^ Dong Hyuk Woo, Nak Hee Seong, Dean L. Lewis, and Hsien-Hsin S. Lee. "An Optimized 3D-Stacked Memory Architecture by Exploiting Excessive, High-Density TSV Bandwidth". In Proceedings of the 16th International Symposium on High-Performance Computer Architecture, pp. 429–440, Bangalore, India, January 2010.

- ^ "Predicting the Performance of a 3D Processor-Memory Chip Stack" Jacob, P., McDonald, J.F. et al.Design & Test of Computers, IEEE Volume 22, Issue 6, Nov.–Dec. 2005 Page(s):540–547

- ^ A. Palesko, The Cost of 3D ICs, 3D InCites Knowledge Portal, January 9, 2015 "The Cost of 3D ICs". 2015-01-09. Archived from the original on 2015-01-09. Retrieved 2015-01-09.

- ^ MazikMedia, Inc, publisher, sites maintained by jamagination (www.jamagination.com). "Robert Patti, "Impact of Wafer-Level 3D Stacking on the Yield of ICs". Future Fab Intl. Volume 23, 2007". Future-fab.com. Archived from the original on 2014-05-17. Retrieved 2014-05-15.

{{cite web}}: CS1 maint: multiple names: authors list (link) - ^ أ ب Hsien-Hsin S. Lee and Krishnendu Chakrabarty, "Test challenges for 3D integrated circuits", IEEE Design and Test of Computers, Special issue on 3D IC Design and Test, vol. 26, no. 5, pp. 26–35, Sep/Oct 2009

- ^ ""EDA's big three unready for 3D chip packaging". EE Times Asia, October 25, 2007". Eetasia.com. Archived from the original on July 18, 2008. Retrieved 2014-05-15.

- ^ أ ب ت ث D. H. Kim, S. Mukhopadhyay, S. K. Lim, "Through-silicon-via aware interconnect prediction and optimization for 3D stacked ICs", in Proc. of Int. Workshop Sys.-Level Interconn. Pred., 2009, pp. 85–92.

- ^ S. Borkar, "3D integration for energy efficient system design", in Proc. Design Autom. Conf., 2011, pp. 214–219.

- ^ ""3-D chip stacks standardized". EE Times November 7, 2008". Eetimes.com. 2014-05-09. Archived from the original on September 30, 2012. Retrieved 2014-05-15.

- ^ ""SEMI International Standards Program Forms 3D Stacked IC Standards Committee". SEMI press release December 7, 2010". Semi.org. 2010-12-07. Archived from the original on May 17, 2014. Retrieved 2014-05-15.

- ^ ""ADVANCED PACKAGING: 3D TSV Technologies Scenarios: Via First or Via Last? 2010 report". Yole report, 2010". I-micronews.com. 2010-01-01. Archived from the original on 2014-05-17. Retrieved 2014-05-15.

- ^ "Si, glass interposers for 3D packaging: analysts' takes". Advanced Packaging August 10, 2010 Archived مارس 14, 2011 at the Wayback Machine

- ^ أ ب J. Knechtel, I. L. Markov, J. Lienig, "Assembling 2D Blocks into 3D Chips" Archived 2016-03-04 at the Wayback Machine, in IEEE Trans. on CAD of ICs and Systems, vol. 31, no. 2, pp. 228–241, Feb. 2012

- ^ S. Garg, D. Marculescu, "3D-GCP: An analytical model for the impact of process variations on the critical path delay distribution of 3D ICs", in Proc. Int. Symp. Quality Electron. Des., 2009, pp. 147–155

- ^ L. K. Scheffer, "CAD implications of new interconnect technologies", in Proc. Design Autom. Conf., 2007, pp. 576–581.

- ^ Moskowitz, Sanford L. (2016). Advanced Materials Innovation: Managing Global Technology in the 21st century. John Wiley & Sons. pp. 165–167. ISBN 9780470508923.

- ^ U.S. Patent 3٬613٬226

- ^ U.S. Patent 3٬651٬490

- ^ "System-in-Package (SiP)". Toshiba. Archived from the original on 3 April 2010. Retrieved 3 April 2010.

- ^ "TOSHIBA COMMERCIALIZES INDUSTRY'S HIGHEST CAPACITY EMBEDDED NAND FLASH MEMORY FOR MOBILE CONSUMER PRODUCTS". Toshiba. April 17, 2007. Archived from the original on November 23, 2010. Retrieved 23 November 2010.

- ^ "Hynix Surprises NAND Chip Industry". Korea Times. 5 September 2007. Retrieved 8 July 2019.

- ^ "Toshiba Launches the Largest Density Embedded NAND Flash Memory Devices". Toshiba. 7 August 2008. Retrieved 21 June 2019.

- ^ "Toshiba Launches Industry's Largest Embedded NAND Flash Memory Modules". Toshiba. 17 June 2010. Retrieved 21 June 2019.

- ^ أ ب ت Kada, Morihiro (2015). "Research and Development History of Three-Dimensional Integration Technology". Three-Dimensional Integration of Semiconductors: Processing, Materials, and Applications. Springer. pp. 15–8. ISBN 9783319186757.

- ^ أ ب "History: 2010s". SK Hynix. Retrieved 8 July 2019.

- ^ "Samsung Begins Mass Producing World's Fastest DRAM – Based on Newest High Bandwidth Memory (HBM) Interface". news.samsung.com.

- ^ "Samsung announces mass production of next-generation HBM2 memory – ExtremeTech". 19 January 2016.

- ^ Shilov, Anton (December 5, 2017). "Samsung Starts Production of 512 GB UFS NAND Flash Memory: 64-Layer V-NAND, 860 MB/s Reads". AnandTech. Retrieved 23 June 2019.

- ^ Manners, David (30 January 2019). "Samsung makes 1TB flash eUFS module". Electronics Weekly. Retrieved 23 June 2019.

- ^ Tallis, Billy (October 17, 2018). "Samsung Shares SSD Roadmap for QLC NAND And 96-layer 3D NAND". AnandTech. Retrieved 27 June 2019.

- ^ "Intel unveils a groundbreaking way to make 3D chips". Engadget.

خطأ استشهاد: الوسم <ref> ذو الاسم "AutoRE-1" المُعرّف في <references> غير مستخدم في النص السابق.

خطأ استشهاد: الوسم <ref> ذو الاسم "AutoRE-2" المُعرّف في <references> غير مستخدم في النص السابق.

خطأ استشهاد: الوسم <ref> ذو الاسم "AutoRE-3" المُعرّف في <references> غير مستخدم في النص السابق.

خطأ استشهاد: الوسم <ref> ذو الاسم "AutoRE-4" المُعرّف في <references> غير مستخدم في النص السابق.

<ref> ذو الاسم "AutoRE-31" المُعرّف في <references> غير مستخدم في النص السابق.المراجع

- JEDECが「DDR4」とTSVを使う「3DS」メモリ技術の概要を明らかに - 後藤弘茂のWeekly海外ニュース Impress Watch Co. (issued:2011-11-08, 2011-11-08)

- 貫通電極を用いたチップ積層技術の開発(Japanese) - oki technical review #211 Vol.74 #3 (issued:2007-10, 2011-11-08)

- TSV(Through Silicon Via:Si貫通電極)(Japanese) - Akita Elpida Memory, inc (2011-11-08)

قراءة متعمقة

- Philip Garrou, Christopher Bower, Peter Ramm: Handbook of 3D Integration, Technology and Applications of 3D Integrated Circuits Vol. 1 and Vol. 2, Wiley-VCH, Weinheim 2008, ISBN 978-3-527-32034-9.

- Yuan Xie, Jason Cong, Sachin Sapatnekar: Three-Dimensional Integrated Circuit Design: Eda, Design And Microarchitectures, Publisher: Springer, ISBN 1-4419-0783-1, ISBN 978-1-4419-0783-7, 978-1441907837, Publishing Date: Dec. 2009.

- Philip Garrou, Mitsumasa Koyanagi, Peter Ramm: Handbook of 3D Integration, 3D Process Technology Vol. 3, Wiley-VCH, Weinheim 2014, ISBN 978-3-527-33466-7.

- Paul D. Franzon, Erik Jan Marinissen, Muhannad S. Bakir, Philip Garrou, Mitsumasa Koyanagi, Peter Ramm: Handbook of 3D Integration: "Design, Test, and Thermal Management of 3D Integrated Circuits", Vol. 4, Wiley-VCH, Weinheim 2019, ISBN 978-3-527-33855-9.

روابط خارجية

- Euronymous (2007-05-02). "3D Integration: A Revolution in Design". Real World Technologies. Retrieved 2014-05-15.

- Semiconductors (2006). "Mapping progress in 3D IC integration". Solid State Technology. Retrieved 2014-05-15.

- Peter Ramm; et al. (2010-09-16). "3D Integration Technology: Status and Application Development". 2010 Proceedings of ESSCIRC. IEEE. pp. 9–16. doi:10.1109/ESSCIRC.2010.5619857. hdl:11250/2463188. ISBN 978-1-4244-6664-1.

- Mingjie Lin; Abbas El Gamal; Yi-chang Lu; Simon Wong (2006-02-22). "Performance Benefits of Monolithically Stacked 3D-FPGA (invited)". IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. Portal.acm.org. 26 (2): 113. doi:10.1145/1117201.1117219. ISBN 978-1595932921.

{{cite journal}}: Unknown parameter|last-author-amp=ignored (|name-list-style=suggested) (help) - "Joint Project for Mechanical Qualification of Next Generation High Density Package-on-Package (PoP) with Through Mold Via Technology". Retrieved 2014-05-15.[dead link]

- "Advancements in Stacked Chip Scale Packaging (S-CSP), Provides System-in-a-Package Functionality for Wireless and Handheld Applications". Retrieved 2014-05-15.[dead link]

- Smith, Lee (July 6, 2010). "Achieving the 3rd Generation From 3D Packaging to 3D IC Architectures". Future Fab International. Amkor Technology. Retrieved 2014-05-15.[dead link]

- "Factors Affecting Electromigration and Current Carrying Capacity of Flip Chip and 3D IC Interconnects". Retrieved 2014-05-15.[dead link]

- "Evaluation for UV Laser Dicing Process and its Reliability for Various Designs of Stack Chip Scale Package". Retrieved 2014-05-15.[dead link]

- "High Density PoP (Package-on-Package) and Package Stacking Development". Retrieved 2014-05-15.[dead link]

- "3D Interconnect Technology Coming to Light". EDN. 2004. Archived from the original on 2008-12-03. Retrieved 2008-01-22.

- "Three-dimensional SoCs perform for future". EE Design. 2003. Retrieved 2014-05-15.

- "MagnaChip, Tezzaron form partnership for 3D chips". EE Times. 2004.[dead link]

- "Matrix preps 64-Mbyte write-once memory". EE Times. 2001. Archived from the original on 2008-05-15. Retrieved 2014-05-15.

- "Samsung starts mass producing first 3D vertical NAND flash, August 2013". Electroiq.com. 2013-08-06. Archived from the original on 2013-08-18. Retrieved 2014-05-15.

- "CEA Leti placed monolithic 3D as the next generation technology as alternative to dimension scaling, August 2013". Electroiq.com. Archived from the original on 2013-08-19. Retrieved 2014-05-15.

- "3D integration: A status report". 2009. Archived from the original on 2013-01-22. Retrieved 2011-01-21.

- Deepak C. Sekar; Zvi Or-Bach. "Monolithic 3D-ICs with Single Crystal Silicon Layers" (PDF). Retrieved 2014-05-15.

{{cite web}}: Unknown parameter|lastauthoramp=ignored (|name-list-style=suggested) (help) - "Global 3D Chips/3D IC Market to Reach US$5.2 Billion by 2015". PRWeb. 2010. Retrieved 2014-05-15.

- "Samsung Develops 30nm-class 32GB Green DDR3 for Next-generation Servers, Using TSV Package Technology". Samsung.com. 2011. Retrieved 2014-05-15.

- "How Might 3-D ICs Come Together?". Semiconductor International. 2008. Archived from the original on 2010-03-04. Retrieved 2009-06-11.

- "Three-Dimensional ICs Solve the Interconnect Paradox". Semiconductor International. 2005. Archived from the original on 2008-02-12. Retrieved 2008-01-22.

- "Ziptronix, Raytheon Prove 3-D Integration of 0.5 µm CMOS Device". Semiconductor International. 2007. Archived from the original on 2007-11-06. Retrieved 2008-01-22.

- Peter Ramm; Armin Klumpp; Josef Weber; Maaike Taklo (2010). "3D System-on-Chip Technologies for More than Moore Systems". Journal of Microsystem Technologies. Springerlink.com. 16 (7): 1051–1055. doi:10.1007/s00542-009-0976-1.

- Philip Garrou, James Lu; Peter Ramm (2012). "Chapter 15". Three-Dimensional Integration. Wiley-VCH. Retrieved 2014-05-15.

{{cite book}}:|work=ignored (help); Unknown parameter|lastauthoramp=ignored (|name-list-style=suggested) (help)

قالب:Emerging technologies in information and communications