قانون مور

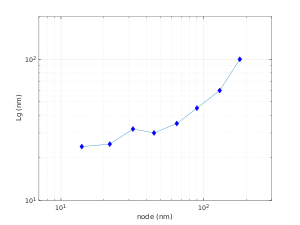

| عمليات تصنيع أشباه الموصلات |

|---|

|

|

MOSFET scaling (process nodes) |

|

|

المستقبل

|

| دراسات المستقبل |

|---|

|

| المفاهيم |

| التقنيات |

| تقييم وتوقع التكنولوجيا |

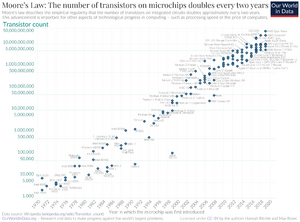

قانون مور Moore's law، هو ملاحظة مفادها أن عدد الترانزستورات في الدائرة المتكاملة يتضاعف كل عامين تقريباً. قانون مور هو رصد وتنبؤ لتوجه تاريخي، أكثر من كونه قانون فيزيائي، وهو علاقة تجريبية مرتبطة باكتساب الخبرة من المنتج.

سُمي القانون على اسم جوردون مور، الشريك المؤسس لشركتي فيرتشايلد لأشباه الموصلات وإنتل (والمدير التنفيذي السابق لإنتل)، الذي افترض عام 1965، أن عدد المكونات في الدائرة المتكاملة يتضاعف كل عام،[أ] وتوقعوا أن يستمر معدل النمو هذا لعقد آخر على الأقل. عام 1975، متطلعًا إلى العقد التالي، قام بمراجعة التوقعات ليخلص إلى أن عدد المكونات في الدائرة المتكاملة يتضاعف كل عامين، معدل النمو السنوي المركب (CAGR) بنسبة 41%. في حين أن مور لم يستخدم الأدلة التجريبية في التنبؤ بأن التوجه التاريخي سيستمر، إلا أن توقعه استمر منذ عام 1975 وأصبح يعرف منذ ذلك الحين باسم "قانون مور".

استخدم تنبؤ مور في صناعة أشباه الموصلات لتوجيه التخطيط طويل المدى ولتحديد أهداف البحث والتطوير، وبالتالي يعمل إلى حد ما باعتباره نبوءة تحقق ذاتها. التقدم في مجال الإلكترونيات الرقمية، مثل إعادة إنتاج أسعار المعالجات الدقيقة معدلة حسب الجودة، زيادة سعة الذاكرة (العشوائية والوميضية)، يتبط تحسين المستشعرات وحتى عدد وحجم البكسل في الكاميرا الرقمية بقوة بواسطة قانون مور. كانت هذه التغييرات المستمرة في الإلكترونيات الرقمية قوة دافعة للتغيير التكنولوجي والاجتماعي، الإنتاجية، والنمو الاقتصادي.

لم يتوصل خبراء الصناعة إلى توافق في الآراء بشأن موعد توقف تطبيق قانون مور تحديداً. أفاد مهندسو المعالجات الدقيقة أن تقدم أشباه الموصلات قد تباطأ على مستوى الصناعة منذ حوالي عام 2010، أقل قليلاً من الوتيرة التي توقعها قانون مور. في سبتمبر 2022 اعتبر ينسن هوانج، الرئيس التنفيذي لشركة إنڤيديا، قانون مور ميتاً،[2] بينما تبنى بات جلسنجر، الرئيس التنفيذي لشركة إنتل، وجهة النظر المعاكسة.[3]

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

التاريخ

عام 1959، قام دوجلاس إنجلبارت بدراسة التصغير المتوقع لحجم الدائرة المتكاملة ونشر نتائجه في مقالة بعنوان "الإلكترونيات الدقيقة وفن التشابه".[4][5][6] قدم إنجلبارت استنتاجاته في المؤتمر الدولي لدوائر الحالة الصلبة، حيث كان مور موجوداً بين الحضور.[7]

عام 1965، طُلب من جوردون مور، الذي كان يعمل في ذلك الوقت مديرًا للبحث والتطوير في فيرتشايلد لأشباه الموصلات، المساهمة في عدد الذكرى السنوية الخامسة والثلاثين من "مجلة الإلكترونيات" مع تنبؤ بمستقبل صناعة مكونات أشباه الموصلات على مدى السنوات العشر القادمة. وكان رده مقالاً موجزاً بعنوان "حشر المزيد من المكونات في دوائر متكاملة".[1][8][ب] في مقالته الافتتاحية، تكهن أنه بحلول عام 1975 سيكون من الممكن احتواء ما يصل إلى 6500 مكون على شبه موصل قياسه ربع بوصة مربعة (~ 1.6 سم مربع).

زاد تعقيد الحد الأدنى من تكاليف المكونات بمعدل ضعفين كل عام تقريباً. بالتأكيد على المدى القصير، من المتوقع أن يستمر هذا المعدل، إن لم يكن سيزيد. على المدى الطويل، يكون معدل الزيادة غير مؤكد إلى حد ما، على الرغم من عدم وجود سبب للاعتقاد بأنه لن يظل ثابتًا تقريبًا لمدة 10 سنوات على الأقل.[1]

افترض مور علاقة خوارزمية-خطية بين تعقيد الجهاز (كثافة دارة أعلى بتكلفة منخفضة) والوقت.[11][12]

في مقابلة أجريت عام 2015، أشار مور إلى مقال عام 1965: "... لقد قمت للتو باستقراء جامح قائلًا إنها ستستمر في التضاعف كل عام على مدى السنوات العشر القادمة."[13] يستشهد أحد مؤرخي القانون قانون ستيجلر للمسميات، ليقدم حقيقة أن المضاعفة المنتظمة للمكونات كانت معروفة للعديد من العاملين في هذا المجال.[12]

عام 1974، أدرك روبرت دنارد من آي بي إم تقنية تحجيم موسفت السريع وصياغة ما أصبح يُعرف باسم مقياس دنارد، والذي يصف أنه عندما تصبح ترانزستورات موس أصغر، فإن كثافة الطاقة تبقى ثابتة بحيث يظل استخدام الطاقة متناسبًا مع المساحة.[14][15] تُظهر الأدلة من صناعة أشباه الموصلات أن هذه العلاقة العكسية بين كثافة الطاقة وكثافة المساحة انهارت في منتصف عقد 2000.[16]

في الاجتماع الدولي لمعهد مهندسي الكهرباء والإلكترونيات للأجهزة الإلكترونية، راجع مور معدل توقعاته، [17][18] متنبئاً بتعقيد أشباه الموصلات سيستمر في التضاعف سنويًا حتى عام 1980 تقريبًا، وبعد ذلك سينخفض إلى معدل يتضاعف كل عامين تقريبًا.[18][19][20] حدد العديد من العوامل المساهمة في هذا السلوك الأسي:[11][12]

- * ظهور تكنولوجيا فلز- أكسيد-أشباه موصلات (MOS)

- المعدل الأسي للزيادة في أحجام die، إلى جانب انخفاض الكثافة المعيبة، مما يؤدي إلى أن مصنعي أشباه الموصلات يمكن أن يعملوا مع مساحات أكبر دون أن يفقدوا عوائد التخفيض

- أبعاد أقل دقة

- ما أسماه مور "ذكاء الدائرة والجهاز"

بعد فترة وجيزة من عام 1975، نشر كارفر ميد، الأستاذ في معهد كاليفورنيا للتكنولوجيا مصطلح "قانون مور".[21][22] أصبح قانون مور في النهاية مقبولًا على نطاق واسع كهدف لصناعة أشباه الموصلات، وقد استشهد به مصنعو أشباه الموصلات التنافسيون أثناء سعيهم لزيادة قوة المعالجة. اعتبر مور قانونه الذي يحمل اسمًا مفاجئًا ومتفائلًا: "قانون مور انتهاكاً لقانون مرفي. كل شيء يتحسن أكثر فأكثر."[23] حتى أن هذا الرصد اعتبر نبوءة تحقق ذاتها.[24][25]

غالبًا ما تعتبر فترة المضاعفة 18 شهراً بسبب توقع زميل مور، ديفد هاوس، الرئيس التنفيذي لشركة إنتل. عام 1975، أشار هاوس إلى أن قانون مور المعدل لمضاعفة عدد الترانزستورات كل عامين يعني بدوره أن أداء رقائق الحاسوب سيتضاعف كل 18 شهر تقريباً[26] (مع عدم وجود زيادة في استهلاك الطاقة).[27] رياضيا، تنبأ قانون مور بأن عدد الترانزستورات سيتضاعف كل عامين بسبب تقلص أبعاد الترانزستور والتحسينات الأخرى. نتيجة لتقلص الأبعاد، توقع مقياس دنارد أن يظل استهلاك الطاقة لكل وحدة مساحة ثابتًا. بدمج هذه التأثيرات، استنتج ديفد هاوس أن أداء رقائق الحاسوب سيتضاعف كل 18 شهر تقريباً. أيضًا نظرًا لتوسيع نطاق دنارد، لن يكون هذا الأداء المتزايد مصحوبًا بزيادة الطاقة، أي أن كفاءة استخدام الطاقة لرقائق الحاسوب القائمة على السيليكون تتضاعف كل 18 شهر تقريباً. انتهى مقياس دنارد في عقد 2000.[16]

أظهر كومي لاحقًا أن معدلًا مشابهًا من تحسين الكفاءة سبقت رقائق السيليكون وقانون مور لتقنيات مثل الأنابيب المفرغة.

أفاد مهندسو المعالجات الدقيقة أنه منذ حوالي عام 2010، تباطأ تقدم أشباه الموصلات على مستوى الصناعة دون الوتيرة التي توقعها قانون مور.[16]

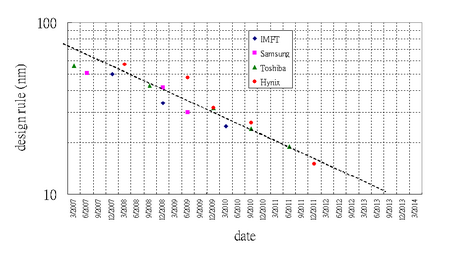

استشهد بريان كرزانيتش، الرئيس التنفيذي السابق لشركة إنتل، بمراجعة مور عام 1975 كسابقة للتباطؤ الحالي، الذي ينتج عن التحديات التقنية وهو "جزء طبيعي من تاريخ قانون مور".[28][29][30] انتهى أيضًا معدل التحسن في الأبعاد المادية المعروفة باسم مقياس دنارد في منتصف عقد 2000. نتيجة لذلك، حولت صناعة أشباه الموصلات تركيزها إلى احتياجات تطبيقات الحوسبة الرئيسية بدلاً من توسيع نطاق أشباه الموصلات.[24][31][16] ومع ذلك، زعمت الشركتان الرائدتان في تصنيع أشباه الموصلات، تايوان لصناعة أشباه الموصلات وسامسونج للإلكترونيات أنهما تواكبان قانون مور[32][33][34][35][36][37] بعقد قدرها 10 نانومتر و7 نانومتر في الإنتاج الضخم[32][33] وعقد بقطر 5 نانومتر في الإنتاج المخاطر، اعتباراً من 2019.[38][39]

قانون مور الثاني

مع انخفاض تكلفة طاقة الحاسوب للمستهلك، تتبع تكلفة استيفاء المنتجين لقانون مور اتجاهًا معاكسًا: زادت تكاليف البحث والتطوير والتصنيع والاختبار بشكل مطرد مع كل جيل جديد من الرقائق. يعد ارتفاع تكاليف التصنيع أحد الاعتبارات المهمة للحفاظ على قانون مور.[40] أدى هذا إلى صياغة قانون مور الثاني، المعروف أيضًا باسم قانون روك (على اسم آرثر روك)، ويفيد بأن تكلفة رأس المال لمصنع أشباه الموصلات تزداد بشكل كبير بمرور الوقت.[41][42]

عوامل التمكين الرئيسية

حافظت ابتكارات العلماء والمهندسين العديدة على قانون مور منذ بداية عصر الدوائر المتكاملة. بعض الابتكارات الرئيسية الواردة أدناه، كأمثلة على الاختراقات التي طورت تكنولوجيا الدوائر المتكاملة وتصنيع النبائط، مما يسمح لعدد الترانزستور بالنمو بأكثر من سبع مرات من حيث الحجم في أقل من خمسة عقود.

- الدائرة المتكاملة (IC) – سبب الوجود لقانون مور. أُخرعت الدائرة المتكاملة الهجين-جرمانيوم بواسطة جاك كيلبي في شركة تكساس إنسترومنتس عام 1958،[43] تلاها اختراع رقاقة دائرة الدائرة المتكاملة المتجانسة-السليكون بواسطة روبرت نويس في فيرتشايلد لأشباه الموصلات عام 1959.[44]

- شبه موصل أكسيد الفلز المكمـِّل (سيموس CMOS) – التي اخترعها تشيه-تانج ساه وفرانك وانلاس في فيرتشايلد لأشباه الموصلات عام 1963.[45][46][47]

- ذاكرة الوصول العشوائي الديناميكية (DRAM) – دورها روبرت دنارد في شركة آي بي إم عام 1967.[48]

- مقاوم الضوء المضخم كيميائياً – اخترعه هيروشي إيتو وجرانت ڤيلسون وج. م. فريشيه في شركة آي بي إم حوالي عام 1980،[49][50][51] التي كانت أكثر حساسية 5-10 أضعاف للأشعة فوق البنفسجية.[52] في منتصف الثمانينيات طرحت آي بي إم مقاوم الضوء المضخم كيميائياً لانتاج ذاكرة الوصول العشوائي الديناميكية.[53][54]

- الطباعة الضوئية بليزر إكسيمر بالأشعة الفوق بنفسجية العميق - اخترعها كانتي جاين[55] في آي بي إم حوالي عام 1980.[56][57][58] قبل هذا، كان ليزر إكسمير يستخدم بصفة رئيسية كأداة بحثية منذ تطويره في السبعينيات.[59][60] من منظور علمي أوسع، تم تسليط الضوء على اختراع الطباعة الضوئية بليزر إكسيمر باعتبارها أحد المعالم الرئيسية في تاريخ الليزر الممتد على مدى 50 عامًا.[61][62]

- اختراعات الربط – اختراعات الربط في أواخر التسعينيات، وتشمل الطلاء الميكانيكي-الكيميائي أو التسوية الميكانيكية-الكيميائية (CMP)، عزل الخنادق، والربط النحاسي- على الرغم من أنها ليسة عاملًا مباشرًا في تصنيع ترانزستورات أصغر - فقد أتاحت تحسين الرقاقات، طبقات الأسلاك المعدنية، تباعد أقرب بين الأجهزة، ومقاومة كهربائية أقل.[63][64][65]

تنبأت خرائط طريق تكنولوجيا صناعة الحاسوب عام 2001 أن قانون مور سيستمر لعدة أجيال من رقائق أشباه الموصلات.[66]

التوجهات الحديثة

أحد التحديات التقنية الرئيسية في هندسة الترانزستورات النانوية المستقبلية هو تصميم البوابات. مع تقلص أبعاد النبيطة، يصبح التحكم في التدفق الحالي في القناة الرفيعة أكثر صعوبة. تأخذ الترانزستورات النانوية الحديثة عادةً شكل موسفت متعدد البوابات، مع كون FinFET هو الترانزستور النانوي الأكثر شيوعًا. يحتوي FinFET على بوابة عازلة على ثلاثة جوانب من القناة. وبالمقارنة فإن هيكل موسفت البوابة الشاملة (GAAFET) لديه تحكم أفضل في البوابة.

- موسفت البوابة الشاملة، عُرض لأول مرة عام 1988، بواسطة فريق توشيبا البحثي بقيادة فوجيو ماسوكا، الذي عرض GAAFET الأسلاك النانوية الرأسي الذي أطلق عليه ماسوكا "ترانزستور البوابة المحيطة" (SGT).[67][68] ماسوكا، الذي يشتهر بكونه مخترع الذاكرة الوميضية، ترك توشيبا لاحقاً وأسس يونيسانتيس للإلكترونيات عام 2004 لبحث تكنولوجيا البوابة المحيطة بالتعاون مع جامعة توهوكو.[69]

- عام 2006، قام فريق باحثين كوريين من معهد كوريا المتقدم للعلوم والتكنولوجيا (KAIST) ومركز نانو فاب الوطني بتطوير ترانزيستور بقطر 3 نانومتر، أصغر نبيطة إلكترونية نانوية في العالم في ذلك الوقت، اعتماداً على تكنولوجياFinFET .[70][71]

- عام 2010، أعلن باحثون من معهد تيندال الوطني في كورك بأيرلندا عن ترانزستور بدون وصلات. يمكن لبوابة تحكم ملفوفة حول سلك نانوي من السيليكون التحكم في مرور الإلكترونات دون استخدام الوصلات أو المحفزات. يزعم الباحثون أنه يمكن إنتاجه بقطر 10 نانومتر باستخدام تقنيات التصنيع الحالية.[72]

- عام 2011، أعلن باحثون في جامعة بيتسبورج عن تطوير ترازستور أحادي الإلكترون، بقطر 1.5 نانومتر، مصنوع من مواد تعتمد على الأكسيد. تتلاقى ثلاثة "أسلاك" على "جزيرة" مركزية يمكنها أن تضم إلكترونًا أو إلكترونين. نفق الإلكترونات من سلك إلى آخر عبر الجزيرة. تؤدي الظروف الموجودة على السلك الثالث إلى خصائص موصلة مميزة بما في ذلك قدرة الترانزستور على العمل كذاكرة الحالة الصلبة.[73] يمكن أن تحفز ترانزستورات الأسلاك النانوية على تصنيع أجهزة حاسوب مجهرية.[74][75][76]

- عام 2012، أعلن فريق بحثي في جامعة نيو ساوث ويلز عن تطوير أول ترانزستور عامل يتألف من ذرة واحدة موضوعة بدقة في بلورة سيليكون (ليس فقط من عينة كبيرة من الترانزستورات العشوائية).[77] تنبأ قانون مور بالوصول إلى هذا الإنجاز بالنسبة للدوائر المتكاملة في المختبر بحلول عام 2020.

- عام 2015، عرضت آي بي إم رقائق بعقدة 7 نانومتر مع ترانزستورات سليكون-جرمانيوم منتجة تستخدم ليثوغرافيا فوق البنفسجية القصوى EUVL. تعتقد الشركة أن كثافة هذا الترانزستور ستكون أكبر بأربع أضعاف كثافة رقاق 14 نانومتر الحالية.[78]

- كانت سامسونك وتايوان لأشباه الموصلات تخططان لتصنيع عقد GAAFET بقطر 3 نانومتر بحلول 2021-2022.[79][80] لاحظ أن أسماء العقد، مثل 3 نانومتر، ليس لها علاقة بالحجم الفيزيائي لعناصر النبيطة (الترانزستورات).

- عام 2001 قام فريق بحثي في شركة توشيبا، من بينهم ت. إيموتو وم. ماتسوي وس.تاكوبو بتطوير عملية ربط رقاقة "وحدة إغلاق الجهاز" لتصنيع حزم دوائر متكاملة ثلاثية الأبعاد (3D IC).[81][82] في أبريل 200، طرحت توشيبا دائرة متكاملة ثلاثية الأبعاد من ثمان طبقات، برقاقة ذاكرة ناند وميضية مضمنة THGAM بسعة 16 ج.ب. التي تم تصنيعها برقائق ناند الوميضية بثمان طبقات بسعة 2 ج.ب.[83] في سبتمبر 2007، طرحت هاينكس دائرة متكاملة ثلاثية الأبعاد بـ24 طبقة، رقاقة ذاكرة وميضية سعة 16 ج.ب. صُنعت برقائق ناند الوميضية بـ24 طبقة مستخدمة عملية ربط الرقائق.[84]

- ف-ناند، تُعرف أيضاً باسم ناند ثلاثية الأبعاد، تسمح لخلايا الذاكرة الوميضية بالارتباط رأسياً مستخدمة تكنولوجيا charge trap flash التي قدمها في الأصل جون سيدون عام 1967، مما أدى إلى زيادة كبيرة في عدد الترانزستورات على شريحة الذاكرة الوميضية. أعلن عن ناند ثلاثية الأبعاد لأول مرة بواسطة توشيبا عام 2007.[85] صُنعت ف-ناند تجارياً لأول مرة بواسطة سامسونگ للإلكترونيات عام 2013.[86][87][88]

- عام 2008، أعلن باحثون في معامل إتش ري عن ممريستور (ذاكرة مقاومة) عامل، عنصر الدائرة السلبية الأساسي الرابع الذي كان وجوده مجرد نظرية من قبل. تسمح الخصائص الفريدة للممريستور بتصنيع أجهزة إلكترونية أصغر، ذات أداء أفضل.[89]

- عام 2014، قام مهندسون في جامعة ستانفورد بتطوير دائرة على نمط العقل البشري. تحاكي رقائق "المركز العصبي" الستة عشر واحد مليون عصب وبلايين الاتصالات المتشابكة، والتي يزعم أنها أسرع 9.000 مرة وكذلك أكثر توفيراً للطاقة عن الحاسوب الشخصي التقليدي.[90]

- عام 2015، أعلنت إنتل وميكرون عن 3D XPoint، ذاكرة مستدامة يزعم أنها أسرع بشكل كبير مع كثافة مماثلة مقارنة بناند. كان من المقرر بدء الإنتاج عام 2016، لكنه تأكل حتى النصف الثاني من 2017.[91][92][93]

- عام 2017، قامت سامسونج بدمج تقنيتها المسماة ف-ناند مع eUFS 3D IC stacking لإنتاج رقاقة ذاكرة مويضية سعة 512 ج.ب، مع ثمانية dies ف-ناند من 64 طبقة.[94] عام 2019، أنتجت سامسونج رقاقة وميضية سعة 1. ت.ب. مع ثمانية dies ف-راند من 96 طبقة، جنباً إلى جنب مع تكنولوجيا الخلية متعددة المستويات (QLC)(حوسبة 4-بيت|4-بيت]] لكل ترانزستور)،[95][96] بما يعادل 2 تريليون ترانزستور، أعلى ترانزستورات في أي شريحة دائرة متكاملة.

- عام 2020، كانت سامسونج للإلكترونيات تخطط لإنتاج عقدة بقطر 5 نانومتر، مستخدمة تكنولوجيا FinFET وEUV.[33][needs update]

- في 21 مايو 2021، أعلنت آي بي إم عن إنشاء أول شريحة حاسوب قطر 2 نانومتر، بأجزاء يفترض أنها أصغر من الحمض النووي البشري.[97]

أفاد مهندسو المعالجات الدقيقة أن تقدم أشباه الموصلات قد تباطأ على مستوى الصناعة منذ حوالي عام 2010 أقل من الوتيرة التي تنبأ بها قانون مور.[16] أعلن بريان كرزانيتش، الرئيس التنفيذي السابق لشركة إنتل، "إن إيقاعنا اليوم أقرب إلى عامين ونصف منه إلى عامين".[98] عام 2015، صرحت إنتل أن التحسينات في نبائط موسفت قد تباطأت، بدءًا من عرض الميزة 22 نانومتر عام 2012، وتستمر حتى 14 نانومتر.[99]

تم الوصول إلى الحدود المادية لتحجيم الترانزستور بسبب تسريب المصدر-الصرف، ومعادن البوابة المحدودة والخيارات المحدودة لمواد القناة. يجري التحقيق في مناهج أخرى لا تعتمد على القياس المادي. يتضمن ذلك حالة الدوران للإلكترون الإلكترونيات السبينية، تقاطعات النفق، والحصر المتقدم لمواد القناة عبر هندسة الأسلاك النانوية.[100] تُطور خيارات الذاكرة المنطق القائمةعلى الإلكترونيات السپينية بنشاط في المختبرات.[101][102]

أبحاث المواد البديلة

تتألف غالبية الترانزستورات الحالية من الدوائر المتكاملة بشكل رئيسي من السيليكون المشوب وسبائكه. ونظراً لأن السيليكون يتم تصنيعه إلى ترانزستورات نانومترية فردية، فإن تأثيرات القنوات القصيرة تؤثر سلباً على الخصائص المادية المطلوبة للسيليكون كترانزستور وظيفي. وفيما يلي عدة بدائل للسيليكون في تصنيع ترانزستورات نانومترية صغيرة.

أحد المواد المقترحة هو "زرنيخيد الإنديوم جاليوم"، أو InGaAs. بالمقارنة مع نظرائها السيليكون والجرمانيوم، تعد ترانزستورات InGaAs أكثر وعودة لتطبيقات المنطق عالية السرعة والطاقة المنخفضة في المستقبل. نظراً للخصائص الأساسية لأشباه الموصلات المركبة III-V، أقترح ترانزستورات المنابع الكمية والتأثير الحقلي التي تعتمد على InGaAs كبدائل لتصاميم الموسفتات التقليدية الأكثر شيوعاً.

- في أوائل عقد 2000، اخترع غشاء high-κ بترسيب الطبقة الذرية وعمليات المحاكاة المزدوجة بواسطة جورتج ساندو في شركة ميكرون تكنولجي، تمديد قانون مور لتقنية سيموس المستوية إلى فئة 30 نانومتر وأصغر.

- عام 2009، أعلنت إنتل عن تطوير ترانزستورات InGaAs بئر كمي بقطر 80 نانومتر. تحتوي أجهزة الآبار الكمومية على مادة محصورة بين طبقتين من المادة مع فجوة نطاق أوسع. على الرغم من كونها ضعف حجم ترانزستورات السيليكون النقي الرائدة في ذلك الوقت، فقد ذكرت الشركة أنها تعمل بنفس الجودة مع استهلاك طاقة أقل.[103]

- عام 2011، أظهر الباحثون في شركة إنتل ترانزستورات InGaAs ثلاثية الأبعاد ثلاثية البوابة مع خصائص تسرب محسنة مقارنةً بالتصميمات المستوية التقليدية. تدعي الشركة أن تصميمها حقق أفضل الكهرباء الساكنة لأي ترانزستور مركب من أشباه الموصلات III-V.[104]

في المؤتمر الدولي لدوائر الحالة الصلبة 2015، أعلنت إنتل عن استخدام مركبات III-V بناءً على مثل هذه البنية لعقدها بقطر 7 نانومتر.[105][106]

- عام 2011، قام باحثون في جامعة تكساس-أوستن بتطوير ترانزستورات InGaAs ذات التأثير المجالي-النفقي، قادرة على تشغيل تيارات أعلى من التصميمات السابقة. عُرض أول تصميمات III-V TFET عام 2009 بواسطة فريق مشترك من جامعة كورنل وجامعة ولاية پنسلڤانيا.[107][108]

- عام 2012، طور فريق في مختبرات ميكروسيستم تكنولوجي التابعة لمعهد مساتشوستس للتكنولوجيا ترانزستور بقطر 22 نانومتر استنادًا إلى InGaAs والذي كان، في ذلك الوقت، أصغر ترانزستور غير سيليكوني صُنع على الإطلاق. استخدم الفريق التقنيات المستخدمة حاليًا في تصنيع أجهزة السيليكون ويهدف إلى تحسين الأداء الكهربائي وتقليل مقياس 10 نانومتر.[109]

تظهر أبحاث الحوسبة البيولوجية أن المواد البيولوجية تتمتع بكثافة معلومات فائقة وكفاءة عالية في استخدام الطاقة مقارنة بالحوسبة القائمة على السيليكون.[110]

تجري دراسة أشكال مختلفة من الجرافين من أجل إلكترونيات الجرافين، على سبيل المثال أظهرت ترانزستور نانوريبون الجرافين نتائج واعدة بشكل كبير منذ ظهوره في المنشورات عام 2008. (يحتوي الجرافين السائب على فجوة نطاق صفرية وبالتالي لا يمكن استخدامه في الترانزستورات بسبب توصيله الثابت، وعدم القدرة على الإيقاف. تقدم الحواف المتعرجة للشرائط النانوية حالات طاقة موضعية في نطاقي التوصيل والتكافؤ، وبالتالي فجوة نطاق تتيح التبديل عند تصنيعها على شكل ترانزستور. وكمثال، GNR نموذجي بعرض 10 نانومتر لديه طاقة فجوة الحزمة المرغوبة من 0.4 eV.[111][112]) ومع ذلك، هناك حاجة للقيام بالمزيد من الأبحاث على طبقات الجرافين دون 50 نانومتر، حيث تزداد قيمته المقاومة وبالتالي تنخفض حركة الإلكترون.[111]

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

التنبؤات وخرائط الطريق

في أبريل 2005، صرح جوردون مور في مقابلة أنه لا يمكن أن يستمر الإسقاط إلى أجل غير مسمى: "لا يمكن أن يستمر إلى الأبد. الطبيعة الأسية هي أنك تدفعهم للخارج وفي النهاية تحدث كارثة". وأشار أيضًا إلى أن الترانزستورات ستصل في النهاية إلى حدود التصغير عند مستويات الذرة

فيما يتعلق بحجم [الترانزستورات]، يمكنك أن ترى أننا نقترب من حجم الذرة وهو ما يمثل حاجزًا أساسيًا، ولكن سيحتاج الأمر إلى جيلين أو ثلاثة جيلين قبل أن نصل إلى هذا الحد - لكن هذا بعيد جدًا عما سبق لنا فعلا. أمامنا من 10 إلى 20 سنة أخرى قبل أن نصل إلى الحد الأساسي. بحلول ذلك الوقت سيكونون قادرين على صنع رقائق أكبر ويكون لدينا ميزانيات ترانزستور بالمليارات.[113]

في عام 2016، أُنتجت خارطة الطريق الدولية لتكنولوجيا لأشباه الموصلات، بعد استخدام قانون مور لقيادة الصناعة منذ عام 1998، أُنتجت خارطة الطريق النهائية. لم تعد تركز خطة البحث والتطوير الخاصة بها على قانون مور. وبدلاً من ذلك، حددت ما يمكن تسميتها بإستراتيجية "أكثر من مور" التي تدفع فيها احتياجات التطبيقات إلى تطوير الرقائق، بدلاً من التركيز على توسيع نطاق أشباه الموصلات. تتراوح برامج تشغيل التطبيقات من الهواتف الذكية إلى الذكاء الاصطناعي إلى مراكز البيانات.[114]

بدأ معهد مهندسي الكهرباء والإلكترونيات في مبادرة رسم خارطة طريق عام 2016، "إعادة تشغيل الحوسبة"، المسماة خارطة الطريق الدولية للأجهزة والأنظمة (IRDS).[115]

معظم المتنبئين، ومن بينهم جوردون مور،[116] من المتوقع أن ينتهي قانون مور بحلول عام 2025.[117][114][118] على الرغم من أن قانون مور سيصل إلى حدود مادية، إلا أن بعض المتنبئين متفائلون بشأن استمرار التقدم التكنولوجي في مجموعة متنوعة من المجالات الأخرى، بما في ذلك معماريات الرقائق الجديدة، والحوسبة الكمومية، والذكاء الاصطناعي والتعلم الآلي.[119][120] أعلن ينسن هوانج، المدير التنفيذي لشركة إنفيديا موت قانون مور عام 2022؛ [2] بعد ذلك بعدة أيام أعلن بات جلسينجر، المدير التنفيذي لشركة إنتل، أن قانون مور لم يمت.[3]

التبعات

ساهمت الإلكترونيات الرقمية في النمو الاقتصادي العالمي في أواخر القرن العشرين وأوائل القرن الحادي والعشرين.[121] القوة الدافعة الأساسية للنمو الاقتصادي هي نمو الإنتاجية،[122] وعوامل قانون مور في الإنتاجية. توقع مور (1995) أن "معدل التقدم التكنولوجي سيتم التحكم فيه من الحقائق المالية".[123] كان من الممكن أن يحدث العكس في أواخر التسعينيات تقريبًا، مع إعلان الاقتصاديين أن "نمو الإنتاجية هو المؤشر الاقتصادي الرئيسي للابتكار".[124] يصف قانون مور القوة الدافعة للتغيير التكنولوجي والاجتماعي والإنتاجية والنمو الاقتصادي.[125][126][122]

ساهم تسارع معدل تقدم أشباه الموصلات في زيادة نمو الإنتاجية بالولايات المتحدة،[127][128][129] التي بلغت 3.4٪ سنويًا في 1997-2004، متجاوزة 1.6٪ سنويًا خلال الفترة 1972-1996 و2005-2013.[130] كما يشير الخبير الاقتصادي ريتشارد أندرسون: "تتبعت العديد من الدراسات سبب تسارع الإنتاجية إلى الابتكارات التكنولوجية في إنتاج أشباه الموصلات التي أدت إلى انخفاض حاد في أسعار هذه المكونات والمنتجات التي تحتوي عليها (بالإضافة إلى توسيع قدرات مثل هذه المنتجات)".[131]

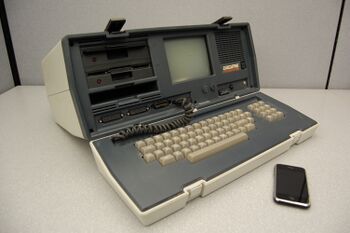

التأثير السلبي الأساسي لقانون مور هو أن التقادم يدفع المجتمع إلى الأمام ضد حدود النمو. مع استمرار "التحسن" السريع للتقنيات، فإنه يجعل التقنيات السابقة عفا عليها الزمن. في المواقف التي يكون فيها أمان واستمرارية الأجهزة أو البيانات أمرًا بالغ الأهمية، أو عندما تكون الموارد محدودة، غالبًا ما يشكل التقادم السريع عقبات أمام العمليات السلسة أو المستمرة.[132]

بسبب البصمة المكثفة للموارد والمواد السامة المستخدمة في إنتاج أجهزة الحاسوب، يؤدي التقادم إلى تأثيرات بيئية ضارة. يتخلص الأمريكيون من 400.000 هاتف محمول يومياً،[133]

لكن هذا المستوى العالي من التقادم يبدو للشركات كفرصة لتوليد مبيعات منتظمة لمعدات جديدة باهظة الثمن، بدلاً من الاحتفاظ بجهاز واحد لفترة أطول من الوقت مما يؤدي إلى استخدام الصناعة التقادم المخطط باعتباره مركز ربح.[134]

هناك مصدر بديل لتحسين الأداء في تقنيات الهندسة الدقيقة التي تستغل نمو عدد الترانزستور المتاح. التنفيذ خارج الترتيب وعلى الرقاقة التخزين المؤقت والجلب المسبق يقللان من اختناق زمن الوصول للذاكرة على حساب استخدام المزيد من الترانزستورات وزيادة تعقيد المعالج. وُصفتهذه الزيادات تجريبياً بواسطة قاعدة بولاك، والتي تنص على أن زيادة الأداء بسبب تقنيات الهندسة المعمارية الدقيقة تقارب الجذر التربيعي لتعقيد (عدد الترانزستورات أو المساحة) المعالج.[135]

لسنوات، قدم صانعو المعالجات زيادات في معدل الساعة والتوازي على مستوى التعليمات، بحيث يتم تنفيذ التعليمات البرمجية ذات الخيوط الواحدة بشكل أسرع على المعالجات الأحدث بدون تعديل.[136] الآن، لإدارة تبديد طاقة وحدة المعالجة المركزية، يفضل صانعو المعالجات تصميمات شرائح متعددة النواة، ويجب كتابة البرامج بطريقة متعددة الخيوط للاستفادة الكاملة من الأجهزة. العديد من نماذج التطوير متعددة الخيوط تقدم النفقات العامة، ولن تشهد زيادة خطية في السرعة مقابل عدد المعالجات. هذا صحيح بشكل خاص أثناء الوصول إلى الموارد المشتركة أو التابعة ، بسبب تنازع القفل. يصبح هذا التأثير أكثر وضوحًا مع زيادة عدد المعالجات. هناك حالات تُرجمت فيها زيادة بنسبة 45٪ تقريبًا في ترانزستورات المعالج إلى زيادة بنسبة 10-20٪ تقريبًا في طاقة المعالجة.[137]

من ناحية أخرى، يضيف المصنعون وحدات معالجة متخصصة للتعامل مع ميزات مثل الرسومات والفيديو والتشفير. على سبيل المثال، لا تضيف امتداد إنتل، جافاسكربت المتوازي دعمًا لمتعددة النوى فحسب، بل تضيف أيضًا ميزات المعالجة غير العامة الأخرى لشرائحها، كجزء من الترحيل في البرمجة النصية من جانب العميل نحو HTML5.[138]

أثر قانون مور على أداء التقنيات الأخرى بشكل كبير: كتب مايكلمالون عن حرب مور بعد النجاح الواضح لعقيدة الصدمة والترويع في أوائل حرب العراق. يعتمد التقدم في تطوير الأسلحة الموجهة على التكنولوجيا الإلكترونية.[139] ساهمت التحسينات في كثافة الدائرة والتشغيل منخفض الطاقة المرتبط بقانون مور أيضًا في تطوير التقنيات بما في ذلك الهواتف المحمولة[140] والطباعة المجسمة.[141]

صيغ أخرى وعمليات رصد مماثلة

تتحسن العديد من مقاييس التكنولوجيا الرقمية بمعدلات أسية ترتبط بقانون مور، بما في ذلك حجم المكونات وتكلفتها وكثافتها وسرعتها. كتب مور فقط عن كثافة المكونات، "المكون هو الترانزستور، المقاوم، الصمام الثنائي أو المكثف"،[123] بأقل تكلفة.

الترانزستورات لكل دائرة متكاملة – الصيغة الأكثر شيوعًا هي مضاعفة عدد الترانزستورات على الدوائر المتكاملة كل عامين. في نهاية السبعينيات، أصبح قانون مور معروفًا بالحد الأقصى لعدد الترانزستورات في أكثر الرقائق تعقيدًا. يوضح الرسم البياني أعلاه أن هذا الاتجاه صحيح اليوم. اعتبارًا من عام 2017، كان المعالج المتاح تجاريًا والذي يمتلك أكبر عدد من الترانزستورات هو سنتريك كور 48 بأكثر من 18 مليار ترانزستور.[142]

الكثافة بأقل تكلفة لكل ترانزستور

هذه هي الصيغة الواردة في بحث مور عام 1965.[1] لا يتعلق الأمر فقط بكثافة الترانزستورات التي يمكن تحقيقها، لكنه يتعلق بكثافة الترانزستورات التي تكون فيها تكلفة الترانزستور هي الأدنى.[143] مع وضع المزيد من الترانزستورات على شريحة، تنخفض تكلفة صنع كل ترانزستور، لكن تزداد فرصة عدم عمل الشريحة بسبب وجود عيب. عام 1965، فحص مور كثافة الترانزستورات التي تنخفض عندها التكلفة إلى الحد الأدنى، ولاحظ أنه نظرًا لتصغير الترانزستورات من خلال التقدم في الطباعة الضوئية، فإن هذا العدد سيزداد "بمعدل ضعفين تقريبًا كل سنة".[1]

مقياس دنارد – يفترض هذا أن استخدام الطاقة سينخفض بالتناسب مع مساحة الترانزستورات (كل من الجهد والتيار متناسبان مع الطول). بالاقتران مع قانون مور، سينمو الأداء لكل واط تقريبًا بنفس معدل كثافة الترانزستور، ويتضاعف كل 1-2 سنة. بحسب دنارد، ستقاس أبعاد الترانزستور بنسبة 30٪ (0.7x) لكل جيل تقني، وبالتالي تقليل مساحتها بنسبة 50٪. سيؤدي ذلك إلى تقليل التأخير بنسبة 30٪ (0.7x) وبالتالي زيادة تردد التشغيل بحوالي 40٪ (1.4x). أخيرًا ، للحفاظ على المجال الكهربائي ثابتًا، سيُقلل الجهد بنسبة 30٪، وتقلل الطاقة بنسبة 65٪ والطاقة (عند تردد 1.4x) بنسبة 50٪. [ت] لذلك، في كل تقنية من الإنتاج تتضاعف كثافة الترانزستور، وتصبح الدائرة أسرع بنسبة 40٪، بينما يظل استهلاك الطاقة كما هو (مع ضعف عدد الترانزستورات).[144] انتهى مقياس دنارد في 2005–2010، بسبب تيارات التسرب.[16]

لا يترجم نمو ترانزستور المعالج الأسي الذي تنبأ به مور دائمًا إلى أداء عملي أكبر لوحدة المعالجة المركزية بشكل كبير. منذ حوالي 2005-2007، انتهى مقياس دنارد، لذلك على الرغم من استمرار قانون مور لعدة سنوات بعد ذلك، إلا أنه لم يحقق أرباحًا في الأداء المحسن.[14][145] السبب الرئيسي الذي استشهد به للانهيار هو أنه في الأحجام الصغيرة، يشكل تسرب التيار تحديات أكبر، كما يتسبب أيضًا في تسخين الشريحة، مما يؤدي إلى خطر الانفلات الحراري وبالتالي زيادة تكاليف الطاقة.[14][145][16]

دفع انهيار مقياس دنارد إلى التركيز بشكل أكبر على المعالجات متعددة النواة، ولكن المكاسب التي يوفرها التحول إلى عدد أكبر من النوى أقل من المكاسب التي يمكن تحقيقها في حالة استمرار مقياس دنارد.[146][147] في خروج آخر عن مقياس دنارد، عام 2012 تبنت معالجات إنتل الدقيقة بوابة FinFET الثلاثية الغير مستوية بقطر 22 نانومتر، لإنتاج ترانزستور أكثر سرعة وأقل في استهلاك الطاقة عن الترانزستور المسطح التقليدي.[148] تباطأ معدل تحسين أداء المعالجات الدقيقة أحادية النواة بشكل ملحوظ.[149] تحسن الأداء أحادي النواة بنسبة 52٪ سنويًا في 1986-2003 و23٪ سنويًا في 2003-2011، لكنه تباطأ إلى 7٪ فقط سنويًا في 2011-2018.[149]

سعر معدات تكنولوجيا المعلومات المعدل حسب الجودة – سعر تكنولوجيا المعلومات، أجهزة الحاسوب والمعدات الطرفية، معدلة-الجودة والتضخم، انخفضت بنسبة 16٪ سنويًا في المتوسط على مدى العقود الخمسة من 1959 حتى 2009.[150][151] ومع ذلك، تسارعت الوتيرة إلى 23٪ سنويًا في 1995-1999 بفضل ابتكار تكنولوجيا المعلومات الأسرع،[124] وتباطأت لاحقاً إلى 2% سنوياً في 2010–2013.[150][152]

بينما يستمر تحسين سعر المعالجات الدقيقة معدلة الجودة،[153] وبالمثل يختلف معدل التحسين، وهو ليس خطيًا على مقياس خوارزمي. تسارع تحسن أسعار المعالجات الدقيقة خلال أواخر التسعينيات، حيث وصل إلى 60٪ سنويًا (النصف كل تسعة أشهر) مقابل معدل التحسن النموذجي بنسبة 30٪ (النصف كل عامين) خلال السنوات السابقة واللاحقة.[154][155] تحسنت المعالجات الدقيقة لأجهزة الحاسوب المحمولة على وجه الخصوص بنسبة 25-35٪ سنويًا في 2004-2010، وتباطأت إلى 15-25٪ سنويًا في 2010-2013.[156]

لا يمكن أن يفسر عدد الترانزستورات لكل شريحة أسعار المعالجات الدقيقة المعدلة الجودة بالكامل.[154][157][158] لا تقصر ورقة مور البحثية لعام 1995 قانون مور على الخطية الصارمة أو تعداد الترانزستور، "لقد حان تعري قانون مور للإشارة إلى أي شيء تقريبًا يتعلق بصناعة أشباه الموصلات في مخطط شبه خوارزمي يقترب من خط مستقيم أتردد في مراجعة أصوله وبذلك أقيد تعريفه".[123]

الكثافة المساحية لمحرك القرص الصلب – أجري تنبؤ مشابه (يُطلق عليه أحيانًا قانون كريدر) عام 2005 الكثافة المساحية لمحرك القرص الصلب.[159]

أعتبر التوقع لاحقًا أنه مفرط في التفاؤل. تباطأت عدة عقود من التقدم السريع في الكثافة المساحية عام 2010 تقريبًا، من 30-100٪ سنويًا إلى 10-15٪ سنويًا، بسبب الضوضاء المرتبطة بحجم الحبيبات الأصغر لوسائط القرص والاستقرار الحراري وقابلية الكتابة باستخدام المجالات المغناطيسية المتاحة.[160][161]

قدرة الألياف-البصرية – يزداد عدد البتات في الثانية التي يمكن إرسالها إلى الألياف الضوئية بشكل كبير، أسرع من قانون مور. قانون كيك، الذي سُمي تكريماً لكيك.[162]

قدرة الشبكة – بحسب جرالد بترز،[163][164] الرئيس السابق لمجموعة لوسنت للشبكات الضوئية مختبرات بيل، هناك نسخة أخرى تسمى قانون بترز للفوتونيات،[165] صياغة تتوازى بشكل متعمد مع قانون مور. ينص قانون بترز على أن كمية البيانات التي تخرج من الألياف الضوئية تتضاعف كل تسعة أشهر.[166] وبالتالي، فإن تكلفة الإرسال قليلاً عبر شبكة بصرية تنخفض بمقدار النصف كل تسعة أشهر. أدى توفر مضاعفة تقسيم الطول الموجي (يُسمى أحيانًا WDM) إلى زيادة السعة التي يمكن وضعها على ألياف مفردة بقدر عامل يصل إلى 100. الشبكات الضوئية ومضاعفة تقسيم الطول الموجي الكثيف (DWDM) يخفض بسرعة تكلفة الشبكات، ويبدو أن تحقيق مزيد من التقدم المضمون. نتيجة لذلك، انهار سعر الجملة لحركة البيانات في فقاعة دوت.كوم. يقول قانون نيلسن أن عرض النطاق الترددي المتاح للمستخدمين يزداد بنسبة 50٪ سنويًا.[167]

البكسلات لكل دولار – وبالمثل، قام باري هندي من كوداك أستراليا بتخطيط البكسل لكل دولار كمقياس أساسي لقيمة الكاميرات الرقمية، مما يدل على الخطية التاريخية (بمقياس سجل) لهذا السوق وفرصة التنبؤ بالاتجاه المستقبلي لسعر الكاميرا الرقمية، شاشات LCD وLED، ودقة الوضوح.[168][169][170][171]

"المعوض القانوني الكبير لمور (TGMLC)"، المعروف أيضًا باسم قانون ويرث - يُشار إليه عمومًا باسم انتفاخ البرمجيات وهو المبدأ الذي يقضي بأن الأجيال المتعاقبة من برامج الحاسوب تزداد حجمًا وتعقيدًا، وبالتالي تعويض مكاسب الأداء التي تنبأ بها قانون مور. في مقال نُشر عام 2008 في إنفوورلد، كتب راندال كندي،[172] موظف سابق في إنتل، يطرح هذا المصطلح باستخدام الإصدارات المتتالية من مايكروسوفت أوفيس بين عامي 2000 و2007 كمقدمة له. على الرغم من المكاسب في أداء الحاسوب خلال هذه الفترة الزمنية وفقًا لقانون مور، قام أوفيس 2007 بأداء نفس المهمة بنصف السرعة على حاسوب عام 2007 النموذجي مقارنةً بأوفيس 2000 على حاسوب عام 2000.

توسيع المكتبة – حُسصبت عام 1945 بواسطة فرمونت ريدر لمضاعفة السعة كل 16 عامًا، إذا توفرت المساحة الكافية.[173] دعا ريدر إلى استبدال الأعمال المطبوعة الضخمة المتحللة بالصور التناظرية المصغرة ميكروفيلم، والتي يمكن نسخها عند الطلب لرواد المكتبات أو المؤسسات الأخرى. لم يتنبأ بالتكنولوجيا الرقمية التي ستتبع بعد عقود لاستبدال الصور الدقيقة التناظرية بالتصوير الرقمي والتخزين ووسائط النقل. سمحت التقنيات الرقمية المؤتمتة التي قد لا تفقد ضياعها بزيادات هائلة في سرعة نمو المعلومات في عصر يُطلق عليه الآن أحيانًا اسم عصر المعلومات.

منحنى كارلسون – هو مصطلح صاغته الإكونومست[174] لوصف المعادل التكنولوجي لقانون مور، وسمي على اسم المؤلف روب كارلسون.[175] تنبأ كارلسون بدقة بأن الوقت المضاعف لتقنيات تسلسل الحمض النووي (يقاس بالتكلفة والأداء) سيكون على الأقل بنفس سرعة قانون مور.[176]

توضح منحنيات كارلسون الانخفاض السريع (في بعض الحالات المفرط في الأداء) في التكلفة، والزيادات في الأداء، لمجموعة متنوعة من التقنيات، بما في ذلك تسلسل الحمض النووي، وتوليف الحمض النووي، ومجموعة من الأدوات الفيزيائية والحاسوبية المستخدمة في التعبير عن البروتين وفي تحديد هياكل البروتين.

قانون إيروم – هي ملاحظة لتطوير العقاقير الصيدلانية تمت كتابتها عمدًا كما ورد في قانون مور إلى الوراء لمقارنتها بالتطورات الهائلة لأشكال التكنولوجيا الأخرى (مثل الترانزستورات) بمرور الوقت. وتنص على أن تكلفة تطوير عقار جديد تتضاعف كل تسع سنوات تقريبًا.

تأثيرات منحى الخبرة - تقول أن كل مضاعفة للإنتاج التراكمي لأي منتج أو خدمة تقريبًا مصحوبة بتخفيض نسبة مئوية ثابتة تقريبية في تكلفة الوحدة. يعود أول وصف نوعي موثق معترف به لهذا التاريخ لعام 1885.[177][178] استخدم منحنى القدرة لوصف هذه الظاهرة في مناقشة لتكلفة الطائرات عام 1936.[179]

قانون إدولم – لاحظ فيل إدولم أن عرض النطاق الترددي لشبكات الاتصالات (بما في ذلك الإنترنت) يتضاعف كل 18 شهرًا.[180]

ارتفع عرض النطاق الترددي لشبكات الاتصال شبكات الاتصالات من بت في الثانية إلى تيرابت في الثانية. يرجع الارتفاع السريع في عرض النطاق الترددي عبر الإنترنت إلى حد كبير إلى نفس مقياس موسفت الذي يمكّن قانون مور، حيث يتم إنشاء شبكات الاتصالات السلكية واللاسلكية من موسفت.[181]

قانون هايتز - يتنبأ بزيادة سطوع مصابيح الليد مع انخفاض تكلفة تصنيعها.

قانون سوانسون - هي ملاحظة أن سعر الوحدات الفولتية الضوئية الشمسية يميل إلى الانخفاض بنسبة 20% لكل مضاعفة لحجم الشحن التراكمي. بالمعدلات الحالية، تنخفض التكاليف بنسبة 75% تقريبًا كل 10 سنوات.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

انظر أيضاً

- تغير متسارع

- ما بعد سيموس

- Ephemeralization

- قانون هوانج

- قانون كومي

- حدود الحوسبة

- خط زمني للمعالجات الدقيقة

- قائمة قوانين التسمية

الهوامش

- ^ The trend begins with the invention of the integrated circuit in 1958. See the graph on the bottom of page 3 of Moore's original presentation of the idea.[1]

- ^ In April 2005, Intel offered US$10,000 to purchase a copy of the original Electronics issue in which Moore's article appeared.[9] كان المهندس المقيم في المملكة المتحدة أول من وجد نسخة وعرضها على شركة إنتل.[10]

- ^ Active power = CV2f

المصادر

- ^ أ ب ت ث ج Moore, Gordon E. (1965-04-19). "Cramming more components onto integrated circuits" (PDF). intel.com. Electronics Magazine. Archived (PDF) from the original on 2019-03-27. Retrieved April 1, 2020.

- ^ أ ب Witkowski, Wallace (2022-09-22). "'Moore's Law's dead,' Nvidia CEO Jensen Huang says in justifying gaming-card price hike" (in الإنجليزية الأمريكية). MarketWatch. Retrieved 2022-09-23.

- ^ أ ب Machkovech, Sam (2022-09-27). "Intel: 'Moore's law is not dead' as Arc A770 GPU is priced at $329" (in الإنجليزية الأمريكية). Ars Technica. Retrieved 2022-09-28.

- ^ Engelbart, Douglas C. (Feb 12, 1960). "Microelectronics and the Art of Similitude". Proceedings of the 1960 International Solid-State Circuits Conference. IEEE. III: 76–77. doi:10.1109/ISSCC.1960.1157297. Archived from the original on Jun 20, 2018.

- ^ Markoff, John (April 18, 2005). "It's Moore's Law But Another Had The Idea First". The New York Times. Archived from the original on March 4, 2012. Retrieved October 4, 2011.

- ^ Markoff, John (August 31, 2009). "After the Transistor, a Leap into the Microcosm". The New York Times. Retrieved 2009-08-31.

- ^ Markoff, John (September 27, 2015). "Smaller, Faster, Cheaper, Over: The Future of Computer Chips". The New York Times. Retrieved September 28, 2015.

- ^ "Excerpts from a conversation with Gordon Moore: Moore's Law" (PDF). Intel Corporation. 2005. p. 1. Archived from the original (PDF) on 2012-10-29. Retrieved 2020-04-01.

- ^ Kanellos, Michael (2005-04-11). "Intel offers $10,000 for Moore's Law magazine". ZDNET News.com. Retrieved 2013-06-21.

- ^ "Moore's Law original issue found". BBC News Online. 2005-04-22. Retrieved 2012-08-26.

- ^ أ ب Schaller, Bob (September 26, 1996). "The Origin, Nature, and Implications of "MOORE'S LAW"". Microsoft. Retrieved September 10, 2014.

{{cite journal}}: Cite journal requires|journal=(help) - ^ أ ب ت Tuomi, I. (2002). "The Lives and Death of Moore's Law". First Monday. 7 (11). doi:10.5210/fm.v7i11.1000.

- ^ Moore, Gordon (March 30, 2015). "Gordon Moore: The Man Whose Name Means Progress, The visionary engineer reflects on 50 years of Moore's Law". IEEE Spectrum: Special Report: 50 Years of Moore's Law (Interview). Interviewed by Rachel Courtland.

We won't have the rate of progress that we've had over the last few decades. I think that's inevitable with any technology; it eventually saturates out. I guess I see Moore's law dying here in the next decade or so, but that's not surprising.

- ^ أ ب ت McMenamin, Adrian (April 15, 2013). "The end of Dennard scaling". Retrieved January 23, 2014.

- ^ Streetman, Ben G.; Banerjee, Sanjay Kumar (2016). Solid state electronic devices. Boston: Pearson. p. 341. ISBN 978-1-292-06055-2. OCLC 908999844.

- ^ أ ب ت ث ج ح خ John L. Hennessy; David A. Patterson (June 4, 2018). "A New Golden Age for Computer Architecture: Domain-Specific Hardware/Software Co-Design, Enhanced Security, Open Instruction Sets, and Agile Chip Development". International Symposium on Computer Architecture – ISCA 2018.

In the later 1990s and 2000s, architectural innovation decreased, so performance came primarily from higher clock rates and larger caches. The ending of Dennard Scaling and Moore's Law also slowed this path; single core performance improved only 3% last year!

- ^ Takahashi, Dean (April 18, 2005). "Forty years of Moore's law". Seattle Times. San Jose, CA. Retrieved April 7, 2015.

A decade later, he revised what had become known as Moore's Law: The number of transistors on a chip would double every two years.

- ^ أ ب Moore, Gordon (1975). "IEEE Technical Digest 1975" (PDF). Intel Corp. Archived (PDF) from the original on 2022-10-09. Retrieved April 7, 2015.

... the rate of increase of complexity can be expected to change slope in the next few years as shown in Figure 5. The new slope might approximate a doubling every two years, rather than every year, by the end of the decade.

{{cite journal}}: Cite journal requires|journal=(help) - ^ Moore, Gordon (2006). "Chapter 7: Moore's law at 40" (PDF). In Brock, David (ed.). Understanding Moore's Law: Four Decades of Innovation. Chemical Heritage Foundation. pp. 67–84. ISBN 978-0-941901-41-3. Archived from the original (PDF) on 2016-03-04. Retrieved March 22, 2018.

- ^ "Over 6 Decades of Continued Transistor Shrinkage, Innovation" (PDF) (Press release). Intel Corporation. May 2011. Archived from the original on 2012-06-17. Retrieved 2023-03-25.

1965: Moore's Law is born when Gordon Moore predicts that the number of transistors on a chip will double roughly every year (a decade later, in 1975, Moore published an update, revising the doubling period to every 2 years)

- ^ Brock, David C., ed. (2006). Understanding Moore's law: four decades of innovation. Philadelphia, Pa: Chemical Heritage Foundation. ISBN 978-0941901413.

- ^ "Moore's Law at 40 – Happy birthday". The Economist. 2005-03-23. Retrieved 2006-06-24.

- ^ أ ب Disco, Cornelius; van der Meulen, Barend (1998). Getting new technologies together. New York: Walter de Gruyter. pp. 206–207. ISBN 978-3-11-015630-0. OCLC 39391108. Retrieved August 23, 2008.

- ^ "Gordon Moore Says Aloha to Moore's Law". the Inquirer. April 13, 2005. Archived from the original on November 6, 2009. Retrieved September 2, 2009.

{{cite web}}: CS1 maint: unfit URL (link) - ^ https://www.pressreader.com/usa/technowize-magazine/20170501/282445643992141. Retrieved 2018-08-24 – via PressReader.

{{cite web}}: Missing or empty|title=(help) - ^ "Moore's Law to roll on for another decade". Retrieved 2011-11-27.

Moore also affirmed he never said transistor count would double every 18 months, as is commonly said. Initially, he said transistors on a chip would double every year. He then recalibrated it to every two years in 1975. David House, an Intel executive at the time, noted that the changes would cause computer performance to double every 18 months.

- ^ Bradshaw, Tim (July 16, 2015). "Intel chief raises doubts over Moore's law". Financial Times. Retrieved 2015-07-16.

- ^ Waters, Richard (July 16, 2015). "As Intel co-founder's law slows, a rethinking of the chip is needed". Financial Times.

- ^ Niccolai, James (July 15, 2015). "Intel pushes 10nm chip-making process to 2017, slowing Moore's Law". Infoworld. Retrieved 2015-07-16.

It's official: Moore's Law is slowing down. ... "These transitions are a natural part of the history of Moore's Law and are a by-product of the technical challenges of shrinking transistors while ensuring they can be manufactured in high volume", Krzanich said.

- ^ Thomas M. Conte; Elie Track; Erik DeBenedictis (December 2015). "Rebooting Computing: New Strategies for Technology Scaling". Computer. 48 (12): 10–13. doi:10.1109/MC.2015.363. S2CID 43750026.

Year-over-year exponential computer performance scaling has ended. Complicating this is the coming disruption of the "technology escalator" underlying the industry: Moore's law.

- ^ أ ب Shilov, Anton (October 23, 2019). "TSMC: 5nm on Track for Q2 2020 HVM, Will Ramp Faster Than 7nm". www.anandtech.com. Retrieved December 1, 2019.

- ^ أ ب ت Shilov, Anton (July 31, 2019). "Home>Semiconductors Samsung's Aggressive EUV Plans: 6nm Production in H2, 5nm & 4nm On Track". www.anandtech.com. Retrieved December 1, 2019.

- ^ Cheng, Godfrey (14 August 2019). "Moore's Law is not Dead". TSMC Blog. TSMC. Retrieved 18 August 2019.

- ^ Martin, Eric (4 June 2019). "Moore's Law is Alive and Well – Charts show it may be dying at Intel, but others are picking up the slack". Medium. Archived from the original on 25 August 2019. Retrieved 19 July 2019.

- ^ "5nm Vs. 3nm". Semiconductor Engineering. 24 June 2019. Retrieved 19 July 2019.

- ^ Lilly, Paul (17 July 2019). "Intel says it was too aggressive pursuing 10nm, will have 7nm chips in 2021". PC Gamer.

- ^ Shilov, Anton. "Samsung Completes Development of 5nm EUV Process Technology". anandtech.com. Retrieved 2019-05-31.

- ^ TSMC and OIP Ecosystem Partners Deliver Industry's First Complete Design Infrastructure for 5nm Process Technology, TSMC, 3 April 2019, https://www.tsmc.com/tsmcdotcom/PRListingNewsAction.do?action=detail&language=E&newsid=THPGWQTHTH, retrieved on 19 July 2019

- ^ Lemon, Sumner; Krazit, Tom (2005-04-19). "With chips, Moore's Law is not the problem". Infoworld. Retrieved 2011-08-22.

- ^ Dorsch, Jeff. "Does Moore's Law Still Hold Up?" (PDF). EDA Vision. Archived from the original (PDF) on 2006-05-06. Retrieved 2011-08-22.

- ^ Schaller, Bob (1996-09-26). "The Origin, Nature, and Implications of "Moore's Law"". Research.microsoft.com. Retrieved 2011-08-22.

- ^ Kilby, J., "Miniaturized electronic circuits", US patent 3138743 , issued June 23, 1964 (filed February 6, 1959).

- ^ Noyce, R., "Semiconductor device-and-lead structure", US patent 2981877 , issued April 25, 1961 (filed July 30, 1959)

- ^ "1963: Complementary MOS Circuit Configuration is Invented". Computer History Museum. Retrieved 6 July 2019.

- ^ (1963) "Nanowatt logic using field-effect metal-oxide semiconductor triodes" in 1963 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. VI: 32–33. doi:10.1109/ISSCC.1963.1157450.

- ^ Wanlass, F., "Low stand-by power complementary field effect circuitry", US patent 3356858 , issued December 5, 1967 (filed June 18, 1963).

- ^ Dennard, R., "Field-effect transistor memory", US patent 3387286 , issued June 4, 1968 (filed July 14, 1967)

- ^ U.S. Patent 4٬491٬628 "Positive and Negative Working Resist Compositions with Acid-Generating Photoinitiator and Polymer with Acid-Labile Groups Pendant From Polymer Backbone" J. M. J. Fréchet, H. Ito and C. G. Willson 1985.[1]

- ^ Ito, H.; Willson, C. G. (1983). "Chemical amplification in the design of dry developing resist material". Polymer Engineering & Science. 23 (18): 204. doi:10.1002/pen.760231807.

- ^ Ito, Hiroshi; Willson, C. Grant; Frechet, Jean H. J. (1982). "New UV resists with negative or positive tone". VLSI Technology, 1982. Digest of Technical Papers. Symposium on.

- ^ Brock, David C. (2007-10-01). "Patterning the World: The Rise of Chemically Amplified Photoresists". Chemical Heritage Magazine. Chemical Heritage Foundation. Retrieved 27 March 2018.

- ^ Lamola, Angelo A., et al. "Chemically amplified resists". Solid State Technology, Aug. 1991, p. 53+."Chemically amplified resists". August 1991. Retrieved 2017-11-01.

- ^ Ito, Hiroshi (2000). "Chemical amplification resists: History and development within IBM" (PDF). IBM Journal of Research and Development. Archived (PDF) from the original on 2022-10-09. Retrieved 2014-05-20.

- ^ 4458994 A USUS 4٬458٬994 A (1984-07-10) Kantilal Jain, Carlton G. Willson, High resolution optical lithography method and apparatus having excimer laser light source and stimulated Raman shifting.

- ^ Jain, K.; Willson, C. G.; Lin, B. J. (1982). "Ultrafast deep-UV lithography with excimer lasers". IEEE Electron Device Letters. 3 (3): 53–55. Bibcode:1982IEDL....3...53J. doi:10.1109/EDL.1982.25476. S2CID 43335574.

- ^ Jain, K. "Excimer Laser Lithography", SPIE Press, Bellingham, WA, 1990.

- ^ La Fontaine, Bruno (October 2010). "Lasers and Moore's Law". SPIE Professional. p. 20.

- ^ Basov, N. G. et al., Zh. Eksp. Fiz. i Tekh. Pis'ma. Red. 12, 473(1970).

- ^ Burnham, R.; Djeu, N. (1976). "Ultraviolet‐preionized discharge‐pumped lasers in XeF, KrF, and ArF". Appl. Phys. Lett. 29 (11): 707. Bibcode:1976ApPhL..29..707B. doi:10.1063/1.88934.

- ^ Lasers in Our Lives / 50 Years of Impact, U.K. Engineering and Physical Sciences Research Council, http://www.stfc.ac.uk/Resources/PDF/Lasers50_final1.pdf, retrieved on 2011-08-22

- ^ "50 Years Advancing the Laser" (PDF). SPIE. Archived (PDF) from the original on 2022-10-09. Retrieved 2011-08-22.

- ^ Moore, Gordon E. (2003-02-10). "transcription of Gordon Moore's Plenary Address at ISSCC 50th Anniversary" in 2003 IEEE International Solid-State Circuits Conference., ISSCC.

- ^ Steigerwald, J. M. (2008). "Chemical mechanical polish: The enabling technology". 2008 IEEE International Electron Devices Meeting. pp. 1–4. doi:10.1109/IEDM.2008.4796607. ISBN 978-1-4244-2377-4. S2CID 8266949. "Table1: 1990 enabling multilevel metallization; 1995 enabling STI compact isolation, polysilicon patterning and yield / defect reduction"

- ^ "IBM100 – Copper Interconnects: The Evolution of Microprocessors". 2012-03-07. Retrieved October 17, 2012.

- ^ "International Technology Roadmap for Semiconductors". Archived from the original on 2011-08-25. Retrieved 2011-08-22.

- ^ Masuoka, Fujio; Takato, H.; Sunouchi, K.; Okabe, N.; Nitayama, A.; Hieda, K.; Horiguchi, F. (December 1988). "High performance CMOS surrounding-gate transistor (SGT) for ultra high density LSIs". Technical Digest., International Electron Devices Meeting: 222–225. doi:10.1109/IEDM.1988.32796. S2CID 114148274.

- ^ Brozek, Tomasz (2017). Micro- and Nanoelectronics: Emerging Device Challenges and Solutions. CRC Press. p. 117. ISBN 9781351831345.

- ^ "Company Profile". Unisantis Electronics. Archived from the original on 22 February 2007. Retrieved 17 July 2019.

- ^ Still Room at the Bottom.(nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology ), 1 April 2006, http://www.highbeam.com/doc/1G1-145838158.html

- ^ Lee, Hyunjin (2006), "Sub-5nm All-Around Gate FinFET for Ultimate Scaling", Symposium on VLSI Technology, 2006: 58–59, doi:, ISBN 978-1-4244-0005-8

- ^ Johnson, Dexter (2010-02-22). "Junctionless Transistor Fabricated from Nanowires". IEEE Spectrum. Retrieved 2010-04-20.

- ^ Cheng, Guanglei; Siles, Pablo F.; Bi, Feng; Cen, Cheng; Bogorin, Daniela F.; Bark, Chung Wung; Folkman, Chad M.; Park, Jae-Wan; Eom, Chang-Beom; Medeiros-Ribeiro, Gilberto; Levy, Jeremy (2011-04-19). "Super-small transistor created: Artificial atom powered by single electron". Nature Nanotechnology. 6 (6): 343–347. Bibcode:2011NatNa...6..343C. doi:10.1038/nnano.2011.56. PMID 21499252. Retrieved 2011-08-22.

- ^ Kaku, Michio (2010). Physics of the Future. Doubleday. p. 173. ISBN 978-0-385-53080-4.

- ^ Yirka, Bob (2013-05-02). "New nanowire transistors may help keep Moore's Law alive". Nanoscale. 5 (6): 2437–41. Bibcode:2013Nanos...5.2437L. doi:10.1039/C3NR33738C. PMID 23403487. Retrieved 2013-08-08.

- ^ "Rejuvenating Moore's Law With Nanotechnology". Forbes. 2007-06-05. Retrieved 2013-08-08.

- ^ Fuechsle, M; Miwa, JA; Mahapatra, S; Ryu, H; Lee, S; Warschkow, O; Hollenberg, LC; Klimeck, G; Simmons, MY (2011-12-16). "A single-atom transistor". Nat Nanotechnol. 7 (4): 242–6. Bibcode:2012NatNa...7..242F. doi:10.1038/nnano.2012.21. PMID 22343383. S2CID 14952278.

- ^ "IBM Reports Advance in Shrinking Chip Circuitry". The Wall Street Journal. July 9, 2015. Retrieved July 9, 2015.

- ^ Armasu, Lucian (11 January 2019), Samsung Plans Mass Production of 3nm GAAFET Chips in 2021, https://www.tomshardware.com/news/samsung-3nm-gaafet-production-2021,38426.html

- ^ Patterson, Alan (October 2, 2017), TSMC Aims to Build World's First 3-nm Fab, https://www.eetimes.com/document.asp?doc_id=1332388

- ^ Garrou, Philip (6 August 2008). "Introduction to 3D Integration" (PDF). Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits. Wiley-VCH. p. 4. doi:10.1002/9783527623051.ch1. ISBN 9783527623051. Archived (PDF) from the original on 2022-10-09.

- ^ Imoto, T.; Matsui, M.; Takubo, C.; Akejima, S.; Kariya, T.; Nishikawa, T.; Enomoto, R. (2001). "Development of 3-Dimensional Module Package, "System Block Module"". Electronic Components and Technology Conference. Institute of Electrical and Electronics Engineers (51): 552–7.

- ^ "TOSHIBA COMMERCIALIZES INDUSTRY'S HIGHEST CAPACITY EMBEDDED NAND FLASH MEMORY FOR MOBILE CONSUMER PRODUCTS". Toshiba. April 17, 2007. Archived from the original on November 23, 2010. Retrieved 23 November 2010.

- ^ "Hynix Surprises NAND Chip Industry". Korea Times. 5 September 2007. Retrieved 8 July 2019.

- ^ "Toshiba announces new "3D" NAND flash technology". Engadget. 2007-06-12. Retrieved 10 July 2019.

- ^ "Samsung Introduces World's First 3D V-NAND Based SSD for Enterprise Applications | Samsung | Samsung Semiconductor Global Website". www.samsung.com.

- ^ Clarke, Peter. "Samsung Confirms 24 Layers in 3D NAND". EETimes.

- ^ "Samsung Electronics Starts Mass Production of Industry First 3-bit 3D V-NAND Flash Memory". news.samsung.com.

- ^ Strukov, Dmitri B; Snider, Gregory S; Stewart, Duncan R; Williams, Stanley R (2008). "The missing memristor found". Nature. 453 (7191): 80–83. Bibcode:2008Natur.453...80S. doi:10.1038/nature06932. PMID 18451858. S2CID 4367148.

- ^ "Stanford bioengineers create circuit board modeled on the human brain – Stanford News Release". news.stanford.edu. 2014-04-28.

- ^ Kelion, Leo (2015-07-28). "3D Xpoint memory: Faster-than-flash storage unveiled". BBC News.

- ^ "Intel's New Memory Chips Are Faster, Store Way More Data". WIRED. July 28, 2015.

- ^ Peter Bright (March 19, 2017). "Intel's first Optane SSD: 375GB that you can also use as RAM". Ars Technica. Retrieved March 31, 2017.

- ^ Shilov, Anton (December 5, 2017). "Samsung Starts Production of 512 GB UFS NAND Flash Memory: 64-Layer V-NAND, 860 MB/s Reads". AnandTech. Retrieved 23 June 2019.

- ^ Manners, David (30 January 2019). "Samsung makes 1TB flash eUFS module". Electronics Weekly. Retrieved 23 June 2019.

- ^ Tallis, Billy (October 17, 2018). "Samsung Shares SSD Roadmap for QLC NAND And 96-layer 3D NAND". AnandTech. Retrieved 27 June 2019.

- ^ IBM (May 6, 2021). "IBM Unveils World's First 2 Nanometer Chip Technology, Opening a New Frontier for Semiconductors". Archived from the original on May 6, 2021. Retrieved May 14, 2021.

- ^ Clark, Don (July 15, 2015). "Intel Rechisels the Tablet on Moore's Law". Wall Street Journal Digits Tech News and Analysis. Retrieved 2015-07-16.

The last two technology transitions have signaled that our cadence today is closer to two and a half years than two

- ^ "INTEL CORP, FORM 10-K (Annual Report), Filed 02/12/16 for the Period Ending 12/26/15" (PDF). Archived from the original (PDF) on 2018-12-04. Retrieved 2017-02-24.

- ^ Nikonov, Dmitri E.; Young, Ian A. (2013-02-01). "Overview of Beyond-CMOS Devices and A Uniform Methodology for Their Benchmarking". Cornell University Library. arXiv:1302.0244. Bibcode:2013arXiv1302.0244N.

{{cite journal}}: Cite journal requires|journal=(help) - ^ Manipatruni, Sasikanth; Nikonov, Dmitri E.; Young, Ian A. (2016). "Material Targets for Scaling All Spin Logic". Physical Review Applied. 5 (1): 014002. arXiv:1212.3362. Bibcode:2016PhRvP...5a4002M. doi:10.1103/PhysRevApplied.5.014002. S2CID 1541400.

- ^ Behin-Aein, Behtash; Datta, Deepanjan; Salahuddin, Sayeef; Datta, Supriyo (2010-02-28). "Proposal for an all-spin logic device with built-in memory". Nature Nanotechnology. 5 (4): 266–270. Bibcode:2010NatNa...5..266B. doi:10.1038/nnano.2010.31. PMID 20190748.

- ^ Dewey, G.; Kotlyar, R.; Pillarisetty, R.; Radosavljevic, M.; Rakshit, T.; Then, H.; Chau, R. (2009-12-07). "Logic performance evaluation and transport physics of Schottky-gate III–V compound semiconductor quantum well field effect transistors for power supply voltages (V<inf>CC</inf>) ranging from 0.5v to 1.0v". Logic performance evaluation and transport physics of Schottky-gate III-V compound semiconductor quantum well field effect transistors for power supply voltages (VCC) ranging from 0.5v to 1.0v. IEEE. pp. 1–4. doi:10.1109/IEDM.2009.5424314. ISBN 978-1-4244-5639-0. S2CID 41734511.

- ^ Radosavljevic R, et al. (2011-12-05). "Electrostatics improvement in 3-D tri-gate over ultra-thin body planar InGaAs quantum well field effect transistors with high-κ gate dielectric and scaled gate-to-drain/gate-to-source separation". Electrostatics improvement in 3-D tri-gate over ultra-thin planar InGaAs quantum well field effect transistors with high-κ gate dielectric and scaled gate-to-drain/gate-to-source separation. IEEE. pp. 33.1.1–33.1.4. doi:10.1109/IEDM.2011.6131661. ISBN 978-1-4577-0505-2. S2CID 37889140.

- ^ Cutress, Ian (2015-02-22). "Intel at ISSCC 2015: Reaping the Benefits of 14nm and Going Beyond 10nm". Anandtech. Retrieved 2016-08-15.

- ^ Anthony, Sebastian (2015-02-23). "Intel forges ahead to 10nm, will move away from silicon at 7nm". Ars Technica. Retrieved 2016-08-15.

- ^ Cooke, Mike (April – May 2011). "InGaAs tunnel FET with ON current increased by 61%" (PDF). Vol. 6, no. 6. Semiconductor Today. Retrieved 2016-08-15.

{{cite news}}: Check date values in:|date=(help) - ^ Han Zhao; et al. (2011-02-28). "Improving the on-current of In0.7Ga0.3As tunneling field-effect-transistors by p++/n+ tunneling junction". Applied Physics Letters. 98 (9): 093501. Bibcode:2011ApPhL..98i3501Z. doi:10.1063/1.3559607.

- ^ Knight, Helen (2012-10-12). "Tiny compound semiconductor transistor could challenge silicon's dominance". MIT News. Retrieved 2016-08-15.

- ^ Cavin, R. K.; Lugli, P.; Zhirnov, V. V. (2012-05-01). "Science and Engineering Beyond Moore's Law". Proceedings of the IEEE. 100 (Special Centennial Issue): 1720–1749. doi:10.1109/JPROC.2012.2190155. ISSN 0018-9219.

- ^ أ ب Avouris, Phaedon; Chen, Zhihong; Perebeinos, Vasili (2007-09-30). "Carbon-based electronics" (PDF). Nature Nanotechnology. 2 (10): 605–15. Bibcode:2007NatNa...2..605A. doi:10.1038/nnano.2007.300. PMID 18654384. Retrieved 2016-08-15.

- ^ Schwierz, Frank (2010-04-11). "Graphene Transistors – A New Contender for Future Electronics". Solid-State and Integrated Circuit Technology (ICSICT), 2010 10th IEEE International Conference.

{{cite journal}}: Cite journal requires|journal=(help) - ^ Dubash, Manek (2005-04-13). "Moore's Law is dead, says Gordon Moore". Techworld. Retrieved 2006-06-24.

- ^ أ ب Waldrop, M. Mitchell (2016-02-09). "The chips are down for Moore's law". Nature. 530 (7589): 144–147. Bibcode:2016Natur.530..144W. doi:10.1038/530144a. ISSN 0028-0836. PMID 26863965.

- ^ "IRDS launch announcement 4 MAY 2016" (PDF). Archived (PDF) from the original on 2016-05-27.

- ^ Cross, Tim. "After Moore's Law". The Economist Technology Quarterly. Retrieved 2016-03-13.

chart: "Faith no Moore" Selected predictions for the end of Moore's law

- ^ Kumar, Suhas (2012). "Fundamental Limits to Moore's Law". arXiv:1511.05956 [cond-mat.mes-hall].

- ^ Smaller, Faster, Cheaper, Over: The Future of Computer Chips NY Times, September 2015

- ^ "The End of More – the Death of Moore's Law". 6 March 2020.

- ^ "These 3 Computing Technologies Will Beat Moore's Law". Forbes.

- ^ Rauch, Jonathan (January 2001). "The New Old Economy: Oil, Computers, and the Reinvention of the Earth". The Atlantic Monthly. Retrieved November 28, 2008.

- ^ أ ب Kendrick, John W. (1961). Productivity Trends in the United States. Princeton University Press for NBER. p. 3.

- ^ أ ب ت Moore, Gordon E. (1995). "Lithography and the future of Moore's law" (PDF). SPIE. Archived (PDF) from the original on 2022-10-09. Retrieved 2014-05-27.

- ^ أ ب Jorgenson, Dale W.; Ho, Mun S.; Samuels, Jon D. (2014). "Long-term Estimates of U.S. Productivity and Growth" (PDF). World KLEMS Conference. Archived (PDF) from the original on 2022-10-09. Retrieved 2014-05-27.

- ^ Keyes, Robert W. (September 2006). "The Impact of Moore's Law". Solid State Circuits Newsletter. Vol. 11, no. 3. pp. 25–27. doi:10.1109/N-SSC.2006.4785857.

- ^ Liddle, David E. (September 2006). "The Wider Impact of Moore's Law". Solid State Circuits Newsletter. 11 (3): 28–30. doi:10.1109/N-SSC.2006.4785858. S2CID 29759395. Archived from the original on 2007-07-13. Retrieved March 25, 2023.

- ^ Jorgenson, Dale W. (2000). "Information Technology and the U.S. Economy: Presidential Address to the American Economic Association". American Economic Association. CiteSeerX 10.1.1.198.9555.

{{cite journal}}: Cite journal requires|journal=(help) - ^ Jorgenson, Dale W.; Ho, Mun S.; Stiroh, Kevin J. (2008). "A Retrospective Look at the U.S. Productivity Growth Resurgence". Journal of Economic Perspectives. 22: 3–24. doi:10.1257/jep.22.1.3.

- ^ Grimm, Bruce T.; Moulton, Brent R.; Wasshausen, David B. (2002). "Information Processing Equipment and Software in the National Accounts" (PDF). U.S. Department of Commerce Bureau of Economic Analysis. Archived (PDF) from the original on 2022-10-09. Retrieved 2014-05-15.

- ^ "Nonfarm Business Sector: Real Output Per Hour of All Persons". Federal Reserve Bank of St. Louis Economic Data. 2014. Retrieved 2014-05-27.

- ^ Anderson, Richard G. (2007). "How Well Do Wages Follow Productivity Growth?" (PDF). Federal Reserve Bank of St. Louis Economic Synopses. Archived (PDF) from the original on 2022-10-09. Retrieved 2014-05-27.

- ^ Sandborn, Peter (April 2008). "Trapped on Technology's Trailing Edge". IEEE Spectrum. Retrieved 2011-11-27.

- ^ Proctor, Nathan (December 11, 2018). "Americans Toss 151 Million Phones A Year. What If We Could Repair Them Instead?". wbur.org. Retrieved July 29, 2021.

{{cite web}}: CS1 maint: url-status (link) - ^ "WEEE – Combating the obsolescence of computers and other devices". SAP Community Network. 2012-12-14. Retrieved 2013-08-08.

- ^ Shekhar Borkar, Andrew A. Chien (May 2011). "The Future of Microprocessors". Communications of the ACM. 54 (5): 67–77. doi:10.1145/1941487.1941507.

- ^ See Herb Sutter,The Free Lunch Is Over: A Fundamental Turn Toward Concurrency in Software, Dr. Dobb's Journal, 30(3), March 2005. Retrieved November 21, 2011.

- ^ Shimpi, Anand Lal (2004-07-21). "AnandTech: Intel's 90nm Pentium M 755: Dothan Investigated". Anadtech. Retrieved 2007-12-12.

- ^ "Parallel JavaScript". Intel. 2011-09-15. Retrieved 2013-08-08.

- ^ Malone, Michael S. (March 27, 2003). "Silicon Insider: Welcome to Moore's War". ABC News. Retrieved 2011-08-22.

- ^ Zygmont, Jeffrey (2003). Microchip. Cambridge, MA, USA: Perseus Publishing. pp. 154–169. ISBN 978-0-7382-0561-8.

- ^ Lipson, Hod (2013). Fabricated: The New World of 3D Printing. Indianapolis, IN, USA: John Wiley & Sons. ISBN 978-1-118-35063-8.

- ^ "Qualcomm Processor". Qualcomm. 2017-11-08.

- ^ Stokes, Jon (2008-09-27). "Understanding Moore's Law". Ars Technica. Retrieved 2011-08-22.

- ^ Borkar, Shekhar; Chien, Andrew A. (May 2011). "The Future of Microprocessors". Communications of the ACM. 54 (5): 67. CiteSeerX 10.1.1.227.3582. doi:10.1145/1941487.1941507. S2CID 11032644. Retrieved 2011-11-27.

- ^ أ ب Bohr, Mark (January 2007). "A 30 Year Retrospective on Dennard's MOSFET Scaling Paper" (PDF). Solid-State Circuits Society. Archived (PDF) from the original on 2013-11-11. Retrieved January 23, 2014.

- ^ Esmaeilzedah, Hadi; Blem, Emily; St. Amant, Renee; Sankaralingam, Kartikeyan; Burger, Doug. "Dark Silicon and the end of multicore scaling" (PDF). Archived (PDF) from the original on 2022-10-09.

- ^ Hruska, Joel (February 1, 2012). "The death of CPU scaling: From one core to many — and why we're still stuck". ExtremeTech. Retrieved January 23, 2014.

- ^ Mistry, Kaizad (2011). "Tri-Gate Transistors: Enabling Moore's Law at 22nm and Beyond" (PDF). Intel Corporation at semiconwest.org. Archived from the original (PDF) on 2015-06-23. Retrieved 2014-05-27.

- ^ أ ب John L. Hennessy; David A. Patterson (June 4, 2018). "A New Golden Age for Computer Architecture: Domain-Specific Hardware/Software Co-Design, Enhanced Security, Open Instruction Sets, and Agile Chip Development" (PDF). International Symposium on Computer Architecture – ISCA 2018. Archived (PDF) from the original on 2022-10-09.

End of Growth of Single Program Speed?

- ^ أ ب "Private fixed investment, chained price index: Nonresidential: Equipment: Information processing equipment: Computers and peripheral equipment". Federal Reserve Bank of St. Louis. 2014. Retrieved 2014-05-12.

- ^ Nambiar, Raghunath; Poess, Meikel (2011). Transaction Performance vs. Moore's Law: A Trend Analysis. Lecture Notes in Computer Science. Vol. 6417. Springer. pp. 110–120. doi:10.1007/978-3-642-18206-8_9. ISBN 978-3-642-18205-1. S2CID 31327565.

- ^ Feroli, Michael (2013). "US: is I.T. over?" (PDF). JPMorgan Chase Bank NA Economic Research. Archived (PDF) from the original on 2014-05-17. Retrieved 2014-05-15.

- ^ (March 2013) "Is the Information Technology Revolution Over?" in Finance and Economics Discussion Series Divisions of Research & Statistics and Monetary Affairs Federal Reserve Board., Federal Reserve Board Finance and Economics Discussion Series (FEDS). "technical progress in the semiconductor industry has continued to proceed at a rapid pace ... Advances in semiconductor technology have driven down the constant-quality prices of MPUs and other chips at a rapid rate over the past several decades."

- ^ أ ب Aizcorbe, Ana; Oliner, Stephen D.; Sichel, Daniel E. (2006). "Shifting Trends in Semiconductor Prices and the Pace of Technological Progress". The Federal Reserve Board Finance and Economics Discussion Series. Retrieved 2014-05-15.

- ^ Aizcorbe, Ana (2005). "Why Are Semiconductor Price Indexes Falling So Fast? Industry Estimates and Implications for Productivity Measurement" (PDF). U.S. Department of Commerce Bureau of Economic Analysis. Archived from the original (PDF) on 2017-08-09. Retrieved 2014-05-15.

- ^ Sun, Liyang (2014-04-25). "What We Are Paying for: A Quality Adjusted Price Index for Laptop Microprocessors". Wellesley College. Archived from the original on 2014-11-11. Retrieved 2014-11-07.

... compared with −25% to −35% per year over 2004–2010, the annual decline plateaus around −15% to −25% over 2010–2013.

- ^ Aizcorbe, Ana; Kortum, Samuel (2004). "Moore's Law and the Semiconductor Industry: A Vintage Model" (PDF). U.S. Department of Commerce Bureau of Economic Analysis. Archived (PDF) from the original on 2007-06-05. Retrieved 2014-05-27.

- ^ Markoff, John (2004). "Intel's Big Shift After Hitting Technical Wall". New York Times. Retrieved 2014-05-27.

- ^ Walter, Chip (2005-07-25). "Kryder's Law". Scientific American. (Verlagsgruppe Georg von Holtzbrinck GmbH). Retrieved 2006-10-29.

- ^ Plumer, Martin L.; et al. (March 2011). "New Paradigms in Magnetic Recording". Physics in Canada. 67 (1): 25–29. arXiv:1201.5543. Bibcode:2012arXiv1201.5543P.

- ^ Mellor, Chris (2014-11-10). "Kryder's law craps out: Race to UBER-CHEAP STORAGE is OVER". theregister.co.uk. UK: The Register. Retrieved 2014-11-12.

Currently 2.5-inch drives are at 500GB/platter with some at 600GB or even 667GB/platter – a long way from 20TB/platter. To reach 20TB by 2020, the 500GB/platter drives will have to increase areal density 44 times in six years. It isn't going to happen. ... Rosenthal writes: "The technical difficulties of migrating from PMR to HAMR, meant that already in 2010 the Kryder rate had slowed significantly and was not expected to return to its trend in the near future. The floods reinforced this."

- ^ Jeff Hecht. "Is Keck's Law Coming to an End?". IEEE Spectrum. 2016.

- ^ "Gerald Butters is a communications industry veteran". Forbes.com. Archived from the original on 2007-10-12.

- ^ "Board of Directors". LAMBDA OpticalSystems. Retrieved 2011-08-22.

- ^ Tehrani, Rich. "As We May Communicate". Tmcnet.com. Retrieved 2011-08-22.

- ^ Robinson, Gail (2000-09-26). "Speeding net traffic with tiny mirrors". EE Times. Archived from the original on 2010-01-07. Retrieved 2011-08-22.

- ^ Nielsen, Jakob (1998-04-05). "Nielsen's Law of Internet Bandwidth". Alertbox. Retrieved 2011-08-22.

- ^ Switkowski, Ziggy (2009-04-09). "Trust the power of technology". The Australian. Retrieved 2013-12-02.

- ^ Sirer, Emin Gün; Farrow, Rik. "Some Lesser-Known Laws of Computer Science" (PDF). Archived (PDF) from the original on 2022-10-09. Retrieved 2013-12-02.

{{cite journal}}: Cite journal requires|journal=(help) - ^ "Using Moore's Law to Predict Future Memory Trends". 2011-11-21. Retrieved 2013-12-02.

- ^ Myhrvold, Nathan (June 7, 2006). "Moore's Law Corollary: Pixel Power". The New York Times. Retrieved 2011-11-27.

- ^ Kennedy, Randall C. (2008-04-14). "Fat, fatter, fattest: Microsoft's kings of bloat". InfoWorld. Retrieved 2011-08-22.

- ^ Rider (1944). The Scholar and the Future of the Research Library. New York City: Hadham Press.

- ^ Life 2.0. (August 31, 2006). The Economist

- ^ Carlson, Robert H. (2010). "Biology Is Technology: The Promise, Peril, and New Business of Engineering Life". Cambridge, MA: Harvard UP.

{{cite journal}}: Cite journal requires|journal=(help) - ^ Carlson, Robert (September 2003). "The Pace and Proliferation of Biological Technologies". Biosecurity and Bioterrorism: Biodefense Strategy, Practice, and Science. 1 (3): 203–214. doi:10.1089/153871303769201851. PMID 15040198. S2CID 18913248.

- ^ Ebbinghaus, Hermann (1913). Memory: A Contribution to Experimental Psychology. Columbia University. p. 42, Figure 2. ISBN 9780722229286.

- ^ Hall, Granville Stanley; Titchene, Edward Bradford (1903). "The American Journal of Psychology".

- ^ Wright, T.P., Factors Affecting the Cost of Airplanes, Journal of Aeronautical Sciences, 3(4) (1936): 122–128.

- ^ Cherry, Steven (2004). "Edholm's law of bandwidth". IEEE Spectrum. 41 (7): 58–60. doi:10.1109/MSPEC.2004.1309810. S2CID 27580722.

- ^ Jindal, R. P. (2009). "From millibits to terabits per second and beyond – Over 60 years of innovation". 2009 2nd International Workshop on Electron Devices and Semiconductor Technology: 1–6. doi:10.1109/EDST.2009.5166093. ISBN 978-1-4244-3831-0. S2CID 25112828.

قراءات إضافية

- Brock, David C. (ed.) (2006). Understanding Moore's Law: Four Decades of Innovation. Philadelphia: Chemical Heritage Foundation. ISBN 0-941901-41-6. OCLC 66463488.

- Mody, Cyrus (2016). The Long Arm of Moore's law: Microelectronics and American Science. Cambridge, Mass.: The MIT Press. ISBN 978-0262035491.

- Thackray, Arnold; David C. Brock, and Rachel Jones (2015). Moore's Law: The Life of Gordon Moore, Silicon Valley's Quiet Revolutionary. New York: Basic Books.

- Tuomi, Ilkka (2002). The lives and death of Moore's Law. First Monday, 7(11), November 2002. https://doi.org/10.5210/fm.v7i11.1000

وصلات خارجية

- Intel press kit – released for Moore's Law's 40th anniversary, with a 1965 sketch by Moore

- No Technology has been more disruptive... Slide show of microchip growth

- Intel (IA-32) CPU speeds 1994–2005 – speed increases in recent years have seemed to slow down with regard to percentage increase per year (available in PDF or PNG format)

- International Technology Roadmap for Semiconductors (ITRS)

- A C|net FAQ about Moore's Law at archive.today (archived 2013-01-02)

- ASML's 'Our Stories', Gordon Moore about Moore's Law, ASML Holding

- CS1 الإنجليزية الأمريكية-language sources (en-us)

- CS1 maint: unfit URL

- CS1 errors: missing title

- CS1 errors: bare URL

- CS1 maint: url-status

- Short description is different from Wikidata

- Articles with hatnote templates targeting a nonexistent page

- Wikipedia articles in need of updating from May 2021

- All Wikipedia articles in need of updating

- Webarchive template archiveis links

- أطروحات 1965

- بيانات عمارة الحاسوب

- الثورة الرقمية

- تاريخ عتاد الحاسوب

- MOSFETs

- قواعد الإبهام

- تغير تكنولوجي

- مسميات