ترانزستور متعدد البوابات

جهاز ملتى جيت multigate أو بوابة الترانزستور ذى التأثير متعدد الحقل (MuGFET ') يشير إلى موسفيت الذي يضم أكثر من بوابة واحدة في جهاز واحد. ويمكن التحكم في بوابات متعددة القطب , حيث البوابة متعددة السطوح تعمل كهربائيا كبوابة وحيدة أو عن طريق بوابة كهربائية مستقلة. ويطلق على الجهاز multigate .توظيف أقطاب بوابة مستقلة في بعض الأحيان بوابة الترانزستور ذى التأثير متعدد الحقل مستقلة أو 'MIGFET الترانزستور Multigate يجري وضعها واحدة من عدة استراتيجيات من قبل CMOS مصنعى أشباه الموصلات لإنشاء معالجات أصغر من أي وقت مضى، و تخزين الحاسوب خلايا الذاكرة, ويشار إليها بالعامية بتمديد قانون مور.[1] المجهودات لتطوير هيتاشي, آى بي إم, إنفينيون تكنولوجيز , إنتل كوربوريشين, تى إس إم سي الترانسستورات متعددة البوابة, تم الإفصاح عنها من قبل أدفانسيد ميكروديفايسس و فريسكيل سيميكونديكتور و يوسي بيركيلي و آخرون و ITRS تنبأت بأن أن هذه الأجهزة سوف تكون حجر الزاوية في sub-32 نانومتر تقنيات.[2]الحاجز الأساسي للتنفيذ على نطاق واسع عملية التصنيع، حيث أن كلا من التصاميم المستوية وغير المستوية , تقدم أو تظهر تحديات , وعلى وجه الخصوص بإعتبارات مثل الطباعة الحجرية والزخرفة. وإستراتيجيات تكميلية أخرى من أجل توسيع نطاق قدرة التكبير أو التصغير للأجهزة وتشمل قناة هندسة الإجهاد, والمعتمدة على تقنيات السيليكون على عازل, و عالية- ك البوابة المعدنية والمواد.

أعلنت شركة إنتل عن اختراق مهم في مسيرة تطور الترانزستور وهو وحدة البناء المجهرية في الإلكترونيات الحديثة، فلأول مرة منذ اختراع ترانزستورات السليكون منذ أكثر من 50 عاما، ستوضع الترانزستورات التي تستخدم بنية ثلاثية الأبعاد في عملية التصنيع بكميات كبيرة. وستطرح إنتل تصميم ترانزستور ثوري ثلاثي الأبعاد يسمى الترانزستور ثلاثي البوابات (Tri-Gate)، وهو ما كانت قد كشفت عنه إنتل أول مرة سنة 2002، لتستخدمه في التصنيع بكميات كبيرة بتقنية «عقدة 22 نانومتر» لاحقاً خلال العام الجاري لإنتاج رقاقة تعرف بالاسم الرمزي آيفي بريدج Ivy Bridge . وستكون معالجات عائلة Intel Core المعتمدة على رقاقات آيفي بريدج هى أول رقاقات تنتج بكميات كبيرة تستخدم الترانزستورات ثلاثية الأبعاد ثلاثية البوابات. ومن المتوقع أن تصبح هذه الرقاقات جاهزة للإنتاج التجاري بنهاية العام الجاري.

تمثل التـــــرانزستورات ثلاثية الأبعـــــاد ثلاثيـــة البوابات انتقالاً جذرياً من البنية المسطحة للترانزستورات ثنائية الأبعاد، والتي تعتبر حتى الآن المكون الأساسي في الحواسيب والهواتف النقالة وأجهزة الإلكترونيات الاستهلاكية، فضلاً عن عناصر التحكم الإلكترونية في السيارات وسفن الفضاء والأجهزة الكهربائية المنزلية والأجهزة الطبية والآلاف من الأجهزة التي نستعملها يومياً منذ عقود من الزمن.

وقال بول أوتيلليني الرئيس والمدير التنفيذي لشركة إنتل:«إن اختراعنا للترانزستورات ثلاثية البوابات وتوظيفها بسرعة ضمن الرقاقات المصنعة بتقنية 22 نانومتر هي نقلة نوعية ستغير المشهد كلياً. ومع الاختراعات الأخرى التي قدمتها إنتل مثل الترانزستورات ذات البوابة المعدنية ومعامل العزل العالي، والسليكون المُجهَد، عامي 2007 و 2003 على التوالي، ستساعد الترانزستورات الجديدة ثلاثية الأبعاد شركة إنتل على تحقيق خفض كبير في استهلاك الطاقة وكذلك في تكلفة تصنيع الترانزستور، وفي الوقت ذاته رفع مستوى الأداء. وسيمكننا ذلك من تصنيع أفضل المنتجات في العالم لكل التطبيقات، من الأجهزة الكفية الصغيرة إلى أسرع الحواسيب الفائقة في العالم».

توفير الطاقة وزيادة الأداء

ترانزستورات إنتل الجديدة ثلاثية الأبعاد ثلاثية البوابات ستمكّن الرقاقات من العمل بتيارات ذات توتر أخفض مع تسرب أقل للطاقة، وتقدم بالتالي جمعاً غير مسبوق بين تحسين مستوى الأداء وكفاءة استهلاك الطاقة مقارنة مع أفضل ترانزستورات الجيل السابق. وهذه الإمكانيات تمنح مصممي الرقاقات مرونة كبيرة لاختيار الترانزستورات الموجهة إما لاستهلاك منخفض للطاقة أو لتحقيق أداء عالٍ، وفقاً للتطبيق المطلوب.

وتقدم الترانزستورات ثلاثية الأبعاد ثلاثية البوابات عيار 22 نانومتر زيادة في الأداء تصل إلى 37% مع تيار ذو توتر منخفض، مقارنة بالترانزستورات المسطحة التي تصنعها إنتل بتقنية 32 نانومتر. هذا التقدم الهائل يعني أنها مثالية للاستخدام في الأجهزة الكفية الصغيرة التي تعمل بطاقة أقل لتنتقل من وضع تشغيل لآخر. أما بالنسبة لاستهلاك الطاقة، فالترانزستورات الجديدة تستهلك أقل من نصف الطاقة عند مستوى الأداء ذاته بالمقارنة مع الترانزستورات المسطحة ثنائية الأبعاد عيار 32 نانومتر.

ويقول مارك بور، وهو باحث أول في شركة إنتل: «إن مكـــــــتسبات تحسين الأداء وتوفير الطاقة لترانزستورات إنتـل الفريدة ثلاثية الأبعاد ثلاثية البوابات تختلف كلياً عن كل ما شاهدناه من قبل. وهذه النقطة المفصلية في تاريخ تطور التقنية تذهب أبعد من مجرد مواكبة قانون مور، فالطاقة المنخفضة والتيار المنخفض التوتر الذي تعمل به هذه الترانزستورات يحققان فوائد تتجاوز كثيراً ما تعودنا رؤيته عند الانتقال من جيل تقنية تصنيع إلى آخر. وهي ستمنح مصممي المنتجات مرونة كبيرة لجعل الأجهزة الحالية أكثر ذكاء، فضلاً عن إتاحة طرح تصاميم جديدة كلياً. ونعتقد أن هذا الإنجاز سيوسع الفارق في الصدارة بين إنتل وبقية الشــــــركات العاملة في صناعة أشباه الموصلات».

الحفاظ على تسارع الابتكارات

ويستمر حجم الترانزستورات في التضاؤل جيلاً بعد جيل، وتصبح أقل تكلفة وأكثر كفاءة في استهلاك الطاقة، وذلك مواكبة لقانون مور ـــ الذي سمي كذلك تيمناً بـ غوردن مور أحد مؤسسي شركة إنتل. لذا، لا تزال إنتل قادرة على مواصلة الابتكار والتكامل، وإضافة مزايا جديدة ونوى معالجة أكثر إلى كل رقاقة، ما يرفع الأداء ويخفض من تكلفة إنتاج الترانزستور الواحد.

وتــــــغدو مسألة المحافظة على التقدم وفق قانون مـــور أكثر تعقــــــيداً مع جيل تـــــقنـــية 22 نانومتر، وعــــلماء الأبحاث في إنتل يدركون ذلك، لذا فإنهم اخترعوا الترانزستور ثلاثي البوابات (Tri-Gate) عام 2002 وقد سمي كذلك لأن البـــــــــوابة لها ثلاثة جوانب.

ويأتي هذا الإعلان اليوم بعد سنوات من التطوير المستمر في خطة إنتل عالية التنسيق بين أقسام البحوث والتطوير والتصنيع، ليضع أخيراً نتـاج هذا العمل حيز التطبيق بهدف تصنيع الرقاقات بتقنية 22 نانومتر بكميات كبيرة.

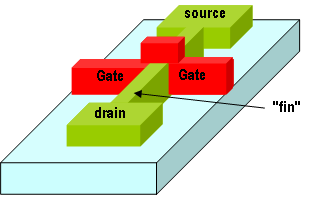

تمثل الترانزستورات ثلاثية الأبعاد ثلاثية البوابات إعادة اختراع للترانزستور. حيث تم استبدال البوابة التقليدية المسطحة ثنائية الأبعاد بوريقة سليكون فائقة النحافة وثلاثية الأبعاد ترتفع عمودياً من قاعدة السليكون. ويتم التحكم بالتيار من خلال وضع بوابة على كل جهة من الجهات الثلاث للوريقة ـــ واحدة من كل جهة وواحدة تمتد على الحافة العلوية لها ـــ بدلاً من بوابة وحيدة فقط على الحافة العلوية كما هو الحال في الترانزستور المسطح ثنائي الأبعاد. ويتيح عنصر التحكم الإضافي مرور أكبر كمية ممكنة للتيار عبر الترانزستور عندما يكون في وضع الوصل (لتحقيق الأداء العالي) ويوقف مرور التيار لما يقرب من الصفر عندما يكون الترانزستور في وضع الإيقاف (لتقليل استهلاك الطاقة)، كما يتيح أيضاً التبديل بسرعة بين الحالتين (من أجل الأداء أيضاً).

كما هو الحال مع ناطحات السحاب التي مكنت مصممي المدن من الاستفادة القصوى من المساحة المتوافرة عبر البناء عمودياً للأعلى، تقدم البنية ثلاثية الأبعاد للترانزستور ثلاثي البوابات من شركة إنتل طريقة للتحكم بكثافة الترانزستورات. وبما أن وريقات السليكون تلك عمودية بطبيعتها، فقد أصبح ممكناً وضع الترانزستورات بشكل أقرب إلى بعضها البعض، وهو أمر أساسي لتحقيق الفوائد التقنية والاقتصادية لقانون مور. ويمكن للمصممين في المستقبل أيضاً متابعة زيادة ارتفاع الوريقات السليكونية وبالتالي الحصول على مكاسب إضافية في الأداء وكفاءة استهلاك الطاقة.

يقول غوردن مور: «على مدى سنوات طويلة، كنا نرى ونعرف الحدود التي ستقف عندها الترانزستورات من حيث تضاؤل الحجم. ويعتبر هذا التغيير في البنية الأساسية مقاربة ثورية حقاً، فهي قادرة على المحافظة على سريان مفعول قانون مور، وعلى مواصلة التسارع التاريخي للابتكارات بشكل مستمر».

متطلبات الصناعة

تعد الترانزستورات المستوية هى الهيكل الأساسى للدوائر المتكاملة لعدة عقود، حيث تراجع بشكل مطرد حجم الترانزستورات الفردية. ونظرا لتناقص حجم الترانزستورات المستوية فإنها تعاني بشكل متزايد من تأثير قصر القناة أو short-channel effect , غير مرغوب فيه، وخاصة "off-state" تسرب التيار مما يزيد من شدة التيار الخامل المطلوبة من قبل الجهاز .[3] في جهاز multigate ، وتحيط القناة بواسطة بوابات عدة على سطوح متعددة، مما يسمح بخمدأكثر فعالية لتسرب التيار "off-state" . بوابات متعددة تسمح أيضا بتيار معزز في حالة "on-state"والمعروف أيضا بدفع التيار . هذه المزايا تترجم إلى انخفاض في استهلاك الطاقة وتعزيز أداء الجهاز.الأجهزة Nonplanar هي أيضا أكثر إحكاما من الترانزستورات المستوية التقليدية، مما يتيح كثافة أعلى للترانزستور الذي يترجم إلى تقليص شامل للميكروإليكترونيات .

التحديات في عمليات الدمج

The primary challenges to integrating nonplanar multigate devices into conventional semiconductor manufacturing processes include:

- Fabrication of a thin silicon "fin" tens of nanometers wide

- Fabrication of matched gates on multiple sides of the fin

Varieties

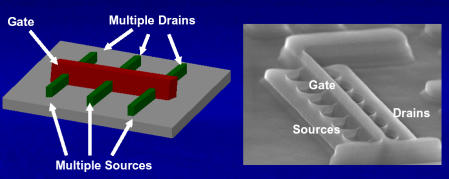

Dozens of multigate transistor variants may be found in the literature. In general, these variants may be differentiated and classified in terms of architecture (planar vs. non-planar design) and number of channels/gates (2, 3, or 4).

Planar double-gate transistors

Planar double-gate transistors employ conventional planar (layer by layer) manufacturing processes to create double-gate devices, avoiding more stringent lithography requirements associated with non-planar, vertical transistor structures. In planar double-gate transistors the channel is sandwiched between two independently fabricated gate/gate oxide stacks. The primary challenge in fabricating such structures is achieving satisfactory self-alignment between the upper and lower gates.[4]

Flexfet

Flexfet is a planar, independently-double-gated transistor with a damascene metal top gate MOSFET and an implanted JFET bottom gate that are self-aligned in a gate trench. This device is highly scalable due to its sub-lithographic channel length; non-implanted ultra-shallow source and drain extensions; non-epi raised source and drain regions; and gate-last flow. Flexfet is a true double-gate transistor in that (1) both the top and bottom gates provide transistor operation, and (2) the operation of the gates is coupled such that the top gate operation affects the bottom gate operation and vice versa.[5] Flexfet was developed, and is manufactured, by American Semiconductor, Inc.

FinFETs

The term FinFET was coined by University of California, Berkeley researchers (Profs. Chenming Hu, Tsu-Jae King-Liu and Jeffrey Bokor) to describe a nonplanar, double-gate transistor built on an SOI substrate,[6] based on the earlier DELTA (single-gate) transistor design.[7] The distinguishing characteristic of the FinFET is that the conducting channel is wrapped by a thin silicon "fin", which forms the gate of the device. The thickness of the fin (measured in the direction from source to drain) determines the effective channel length of the device.

In current usage the term FinFET has a less precise definition. Among microprocessor manufacturers, AMD, IBM, and Motorola describe their double-gate development efforts as FinFET development whereas Intel avoids using the term to describe their closely related tri-gate [1] architecture. In the technical literature, FinFET is used somewhat generically to describe any fin-based, multigate transistor architecture regardless of number of gates.

A 25-nm transistor operating on just 0.7 Volt was demonstrated in December 2002 by Taiwan Semiconductor Manufacturing Company. The "Omega FinFET" design, named after the similarity between the Greek letter "Omega" and the shape in which the gate wraps around the source/drain structure, has a gate delay of just 0.39 picosecond (ps) for the N-type transistor and 0.88 ps for the P-type.

Tri-gate transistors (Intel)

Tri-gate or 3-D are terms used by Intel Corporation to describe their nonplanar transistor architecture planned for use in future microprocessors. These transistors employ a single gate stacked on top of two vertical gates allowing for essentially three times the surface area for electrons to travel. Intel reports that their tri-gate transistors reduce leakage and consume far less power than current transistors. This allows up to 37% higher speed, and a power consumption at under 50% of the previous type of transistors used by Intel.[8]

Intel currently plans to release a new line of CPUs, termed Ivy Bridge, which feature tri-gate transistors. [9] Intel has been working on its tri-gate architecture since 2002, but it took until 2011 to work out mass production issues. The new style of transistor was described on May 5, 2011, in San Francisco.[10] Intel factories are expected to make upgrades over 2011 and 2012 to be able to manufacture the Ivy Bridge CPUs.[11] As well as being used in Intel's Ivy Bridge chips for desktop PCs, the new transistors will also be used in Intel's Atom chips for low powered devices.[10]

In the technical literature, the term tri-gate is sometimes used generically to denote any multigate FET with three effective gates or channels.

Gate-all-around (GAA) FETs

Gate-all-around FETs are similar in concept to FinFETs except that the gate material surrounds the channel region on all sides. Depending on design, gate-all-around FETs can have two or four effective gates. Gate-all-around FETs have been successfully built around silicon nanowire.[12]

انظر أيضاً

الهامش

- ^ Risch, L. "Pushing CMOS Beyond the Roadmap", Proceedings of ESSCIRC, 2005, p. 63

- ^ http://www.itrs.net/Links/2006Update/FinalToPost/04_PIDS2006Update.pdf Table39b

- ^ Subramanian V (2010). "Multiple gate field-effect transistors for future CMOS technologies". IETE Technical Review. 27: 446–454.

- ^ Wong, H-S. Chan, K. Taur, Y. "Self-Aligned (Top and Bottom) Double-Gate MOSFET with a 25 nm Thick Silicon Channel" IEDM 1997, p.427

- ^ Wilson, D.; Hayhurst, R.; Oblea, A.; Parke, S.; Hackler, D. "Flexfet: Independently-Double-Gated SOI Transistor With Variable Vt and 0.5V Operation Achieving Near Ideal Subthreshold Slope" SOI Conference, 2007 IEEE International

- ^ Huang, X. et al. (1999) "Sub 50-nm FinFET: PMOS" International Electron Devices Meeting Technical Digest, p. 67. December 5–8, 1999.

- ^ Hisamoto, D. et al. (1991) "Impact of the vertical SOI 'Delta' Structure on Planar Device Technology" IEEE Trans. Electron. Dev. 41 p. 745.

- ^ Cartwright J (2011). "Intel enters the third dimension". Nature. doi:10.1038/news.2011.274.

- ^ "Intel Reinvents Transistors Using New 3-D Structure". Intel. Retrieved 5/4/2011.

{{cite web}}: Check date values in:|accessdate=(help) - ^ أ ب "Transistors go 3D as Intel re-invents the microchip". Ars Technica. 5 May 2011. Retrieved 7 May 2011.

- ^ "Intel's New Tri-Gate Ivy Bridge Transistors: 9 Things You Need to Know". PC Magazine. 4 May 2011. Retrieved 7 May 2011.

- ^

Singh N; et al. (2006). "High-Performance fully depleted Silicon Nanowire Gate-All-Around CMOS devices". IEEE Electron Device Letters. 27 (5): 383–386. doi:10.1109/LED.2006.873381.

{{cite journal}}: Explicit use of et al. in:|author=(help)