موسفت

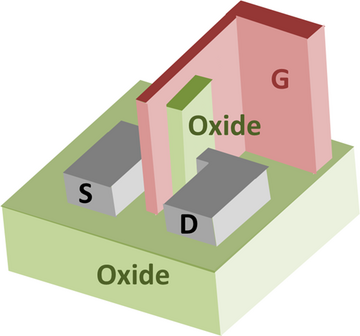

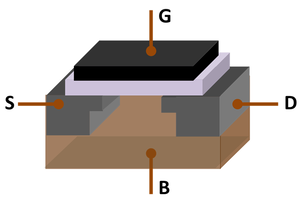

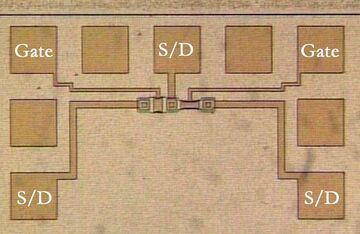

MOSFET, showing gate (G), body (B), source (S) and drain (D) terminals. The gate is separated from the body by an insulating layer (pink). | |

| مبدأ العمل | شبه موصل |

|---|---|

| اِختُرِعَ | 1959 |

| أول انتاج | 1960 |

| ترتيب الدبابيس | gate (G), body (B), source (S) and drain (D) |

| الرمز الإلكتروني | |

| |

ترانزستور الأثر الحقلي للأكاسيد المعدنية لأشباه الموصلات metal–oxide–semiconductor field-effect transistor (MOSFET أو MOS-FET أو MOS FET)، المعروف أيضاً باسم ترانزستور أكسيد السيليكون والمعدن (ترانزستور MOS أو MOS)،[1] وهو نوع من ترانزستور تأثير المجال ذو البوابة المعزولة التي يتم تصنيعها بواسطة الأكسدة المتحكم بها من أشباه الموصلات، عادةً السيليكون. يحدد جهد طرف البوابة التوصيل الكهربائي للجهاز؛ كما يمكن استخدام هذه القدرة على تغيير الموصلية مع مقدار الجهد المطبق من أجل تضخيم أو تبديل الإشارات الإلكترونية.

اختُرع الموسفت بواسطة محمد محمد عطا الله وداوون كانگ في معامل بل في عام 1959، وتم تقديمه لأول مرة في عام 1960. وهو اللبنة الأساسية للإلكترونيات الحديثة، ومن الأجهزة الأكثر تصنيعاً في التاريخ، بإجمالي يقدر بـ 13 sextillion (1.3×1022) تم تصنيعها بين عامي 1960 و2018.[2]كما إنه من عناصر أشباه الموصلات السائدة في الدوائر المتكاملة الرقمية و التناظرية (ICs)،[3] وجهاز الطاقة الأكثر شيوعاً.[4] وهو ترانزستور مضغوط تم تصغيره وإنتاجه بكميات كبيرة من أجل مجموعة واسعة من التطبيقات، مما أحدث ثورة في صناعة الإلكترونيات والاقتصاد العالمي، وكونه مركزاً في الثورة الرقمية وعصر السيليكون و عصر المعلومات. أدى تحجيم الموسفت وتصغيره إلى النمو الأسي السريع لتقنية أشباه الموصلات الإلكترونية منذ الستينيات، وتمكين الدوائر فائقة التكامل مثل شرائح الذاكرة والمعالجات الدقيقة. وتعتبر الموسفتات "العمود الفقري" لصناعة الإلكترونيات.

الميزة الرئيسية للموسفت هي أنها لا تتطلب أي تيار إدخال تقريباً للتحكم في تيار الحمل، عند مقارنتها بترانزستورات ثنائية القطب (BJTs). في موسفتات وضع التعزيز، يمكن للجهد المطبق على طرف البوابة أن يزيد الموصلية من حالة "إيقاف التشغيل العادي". في موسفتات وضع الاستنزاف، يمكن للجهد المطبق عند البوابة أن يقلل الموصلية من حالة "التشغيل العادي".[5] كما تتمتع الموسفتات بقدرة عالية على التوسع، مع زيادة التصغير، ويمكن تصغيرها بسهولة إلى أبعاد أصغر. لديها أيضاً سرعة تحويل أسرع (مثالية لـ للإشارات الرقمية، وحجم أصغر بكثير، وتستهلك طاقة أقل بشكل ملحوظ، وتسمح بكثافة أعلى بكثير (مثالية لدارة متكاملة على نطاق واسع)، مقارنة بـ BJTs. كما أن الترانزستورات الموسفت أرخص ولديها خطوات معالجة بسيطة نسبياً، مما يؤدي إلى ارتفاع عائد التصنيع.

يمكن تصنيع دوائر الموسفت إما كجزء من شرائح دائرة MOS المتكاملة أو كأجهزة موسفت منفصلة (مثل الموسفتات الاستطاعية)، ويمكن أن تتخذ شكل الترانزستورات ذات بوابة واحدة أو متعدد البوابات. نظراً لأن الموسفتات يمكن تصنيعها باستخدام نوع p أو أشباه الموصلات من النوع n ((PMOS أو NMOS logic، على التوالي)، يمكن استخدام أزواج من الموسفتات لإنشاء دوائر تبديل ذات استهلاك الطاقة: CMOS (منطق MOS التكميلي).

يشير الاسم شبه موصل أمسيد المعدن (MOS) عادةً إلى بوابة معدنية، عزل أكسيد، وأشباه الموصلات (عادةً السيليكون).[1] ومع ذلك، فإن "المعدن" في اسم الموسفت هو تسمية خاطئة أحياناً، لأن مادة البوابة يمكن أن تكون أيضاً طبقة من پولي سليكون (سيليكون متعدد الكريستالات). إلى جانب أكسيد، يمكن أيضاً استخدام مواد مختلفة عازلة بهدف الحصول على قنوات قوية بجهد مطبق أصغر. كما أن مكثف MOS هو أيضاً جزء من هيكل الموسفت.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

تاريخ مبكر

خلفية

اقترح الفيزيائي النمساوي يوليوس إدگار ليلينفلد المبدأ الأساسي لترانزستور تأثير المجال (FET) لأول مرة في عام 1926، عندما قدم أول براءة اختراع لترانزستور تأثير حقل ذو بوابة معزولة.[6] على مدار العامين المقبلين، وصف العديد من هياكل FET. في تكوينه، شكل الألمنيوم المعدن وأكسيد الألومنيوم، بينما تم استخدام كبريتيد النحاس كأشباه الموصلات. ومع ذلك، لم يكن قادراً على بناء جهاز فعلي عملي.[7] تم وضع نظرية FET لاحقاً أيضاً من قبل المهندس الألماني أوسكار هيل في ثلاثينيات القرن الماضي والفيزيائي الأمريكي وليام شوكلي في الأربعينيات.[8] لم يكن هناك FET عملي فعلي تم بناؤه في ذلك الوقت، ولم تتضمن أي من مقترحات FET الأولية السيليكون المؤكسد حرارياً.[7]

ركزت شركات أشباه الموصلات في البداية على ترانزستور ثنائي القطب (BJTs) في السنوات الأولى من صناعة أشباه الموصلات. ومع ذلك، كان ترانزستور الوصلة جهازاً ضخماً نسبياً يصعب تصنيعه على أساس الإنتاج بالجملة، مما جعله يقتصر على عدد من التطبيقات المتخصصة. تم وضع نظرية FETs كبدائل محتملة لترانزستورات الوصلات، لكن الباحثين لم يتمكنوا من بناء FETs عملية، ويرجع ذلك إلى حد كبير إلى حاجز الحالة السطحية المزعج الذي منع المجال الكهربائي الخارجي من اختراق المادة.[9] وفي الخمسينيات من القرن الماضي، تخلى الباحثون إلى حد كبير عن مفهوم FET، وركزوا بدلاً من ذلك على تقنية BJT.[10]

في عام 1955، قام كارل فروش ولنكلن ديريك بطريق الخطأ بتغطية سطح رقاقة السيليكون بطبقة من ثاني أكسيد السليكون. في توصيفهم التجريبي اللاحق لطبقة الأكسيد هذه، وجدوا أنها تمنع دخول منشطات معينة إلى رقاقة السيليكون (على الرغم من السماح للآخرين) وبالتالي اكتشفوا تأثير التخميل لطبقة الأكسدة على هذا أشباه الموصلات. أظهر عملهم الإضافي حفر فتحات صغيرة في طبقة الأكسيد لنشر المنشطات في مناطق محكومة بدقة من رقاقة السليكون. في عام 1957، نشروا ورقة بحثية وحصلوا على براءة اختراع لأسلوبهم في تلخيص عملهم. تُعرف التقنية التي طوروها بإخفاء انتشار الأكسيد، والذي سيتم استخدامه لاحقاً في تصنيع أجهزة الموسفتات. في معامل بل، تم إدراك أهمية تقنية فروش على الفور لأن أكاسيد السليكون أكثر ثباتاً من أكاسيد الجرمانيوم، ولها خصائص عازلة أفضل ويمكن استخدامها في نفس الوقت كقناع انتشار. تم توزيع نتائج عملهم في جميع أنحاء معامل بل في شكل مذكرات BTL قبل نشرها في عام 1957. في شبه موصل شوكلي، قام شوكلي بتعميم النسخة التمهيدية لمقالهم في ديسمبر 1956 على جميع كبار موظفيه، بما في ذلك جان هورني.[9][11][12]

الاختراع

تعامل محمد محمد عطاالله في معامل بل مع مشكلة الحالات الخاملة في أواخر الخمسينيات من القرن الماضي. التقط عمل فروش على الأكسدة، محاولًا تخميل السطح من السيليكون من خلال تكوين طبقة الأكسيد فوقه. كان يعتقد أن زراعة نوعية رفيعة جداً وعالية الجودة ازدادت حرارياً SiO

2 فوق رقاقة سيليكون نظيفة من شأنها أن تحيد حالات السطح بما يكفي لصنع ترانزستور عملي ذي تأثير حقلي. كما كتب النتائج التي توصل إليها في مذكراته BTL في عام 1957، قبل تقديم عمله في اجتماع جمعية الكيمياء الكهربية في عام 1958.[13][14][15][16][8] كان هذا تطوراً مهماً مكّن تقنية MOS وشرائح الدوائر المتكاملة من السليكون (IC).[17]في العام التالي، وصف جون مول مكثف MOS في جامعة ستانفورد.[18] تمكن زملاء عطالله في العمل لگنزا وسپتزر، الذين درسوا آلية الأكاسيد المزروعة حرارياً، من تصنيع مكدس Si/SiO2، [7] مع عطا الله وكانگ بالاستفادة من النتائج التي توصلوا إليها.[19][20]

اختُرع الموسفت عندما نجح محمد عطاالله وداوون كانگ[14][13] بتصنيع أول عنصر موسفت في نوفمبر 1959.[21] ويغطي الجهاز براءتي اختراع، قدم كلٌ منهما على حدة من قبل عطا الله وكانگ في مارس 1960.[22][23][24][25]ونشرا نتائجهما في يونيو 1960،[26] في مؤتمر العناصر الصلبة الذي عقد في جامعة كارنگي ملون.[27] في نفس العام، اقترح عطاالله استخدام دوائر الموسفت لبناء رقائق MOS المتكاملة (MOS IC)، مشيراً إلى سهولة تصنيع الموسفت.[9]

التسويق

كانت ميزة الموسفت أنه كان مضغوط نسبياً وسهل الإنتاج بكميات كبيرة مقارنةً بترانزستور الوصلة المستوية،[28] لكن الموسفتات مثلت تقنية جديدة بشكل جذري، كان اعتمادها يتطلب رفض التقدم الذي أحرزه بيل مع ترانزستور ثنائي القطب (BJT). فقد كان الموسفت في البداية أبطأ وأقل موثوقية من BJT.[29]

في أوائل الستينيات، تم إنشاء برامج البحث التكنولوجي MOS بواسطة فيرتشايلد لأشباه الموصلات، مختبرات RCA، جنرال مايكرو إلكترونكس (بقيادة مهندس فيرتشايلد السابق فرانك وانلاس) وآيبيإم.[30] في عام 1962، بنى ستيڤ هوڤشتاين وفريد هايمان في RCA أول رقاقة دائرة متكاملة MOS. في العام التالي، قاموا بجمع جميع الأعمال السابقة على FETs وقدموا نظرية تشغيل الموسفت.[31] تم تطوير CMOS بواسطة تشي-تانگ ساه وفرانك وانلاس في فيرتشايلد عام 1963.[32] تم بناء أول دائرة CMOS متكاملة لاحقاً في عام 1968 بواسطة ألبرت ميدون.[33]

أُصدر أول إعلان رسمي عام عن وجود الموسفت كتقنية محتملة في عام 1963. ثم تم تسويقها لأول مرة بواسطة جنرال مايكروإلترونكس في مايو 1964، وتبع ذلك إعلان فيرتشايلد في أكتوبر 1964. وكان أول عقد MOS لشركة GMe مع ناسا، والذي استخدم الموسفتات لـ للمركبات الفضائية والسواتل في منصة المراقبة بين كوكبية (IMP) وبرنامج إكسپلوررز.[30] كانت الموسفتات المبكرة التي تم تسويقها بواسطة جنرال مايكروإلترونكس وفيرتشايلد عبارة عن قناة p ( PMOS) لتطبيقات المنطق والتبديل.[8] بحلول منتصف الستينيات، كانت RCA تستخدم الموسفتات في منتجاتها الاستهلاكية، بما في ذلك راديو FM والتلفزيون والمضخمات الإلكترونية.[34] في عام 1967، طور باحثو معامل بل روبرت كيروينو دونالد كلاين وجون ساراس ترانزستور MOS [[Self-aligned gate |البوابة ذاتية الانحياز]] (بوابة السيليكون) MOS، والذي استخدمه باحثو فيرتشايلد فيدريكو فاجين وتوم كلاين بتكييفها مع الدوائر المتكاملة في عام 1968.[35]

ثورة الموس

أدى تطوير الموسفت إلى ثورة في تكنولوجيا الإلكترونيات، تسمى ثورة MOS[36] أو ثورة الموسفتات،[37]والذي يغذي النمو التكنولوجي والاقتصادي في وقت مبكر صناعة أشباه الموصلات.

أصبح تأثير الموسفتات مهماً تجارياً من أواخر الستينيات فصاعداً.[38] أدى ذلك إلى ثورة في صناعة الإلكترونيات، والتي أثرت منذ ذلك الحين على الحياة اليومية بكل الطرق تقريباً.[39]تم الاستشهاد باختراع الموسفتات على أنه ولادة الإلكترونيات الحديثة[40]وكانت محورية في ثورة الحواسيب الصغيرة.[41]

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

الأهمية

يشكل الموسفت أساس الإلكترونيات الحديثة،[42] وهو العنصر الأساسي في معظم المعدات الإلكترونية الحديثة.[43] وهو الترانزستور الأكثر شيوعاً في الإلكترونيات،[13] وهو المكون شبه موصل الأكثر استخداماً في العالم.[44]كما تم وصفه بأنه "العمود الفقري لصناعة الإلكترونيات"[45] و "التقنية الأساسية" من أواخر القرن العشرين إلى أوائل القرن الحادي والعشرين.[10] كان تحجيم الموسفت وتصغيره (انظر List of semiconductor scale examples) هي العوامل الأساسية وراء النمو الأسي السريع لتقنية أشباه الموصلات الإلكترونية منذ الستينيات،[46] نظراً لأن التصغير السريع لدوائر الموسفت كان مسؤولاً إلى حد كبير عن زيادة كثافة الترانزستور، وزيادة الأداء وتقليل استهلاك الطاقة لرقائق الدائرة المتكاملة والأجهزة الإلكترونية منذ الستينيات.[47]

لدى الموسفتات قابلية عالية للتوسع (قانون مور ومقياس دنار)،[48] مع زيادة التصغير،[49]كما يمكن تصغيرها بسهولة إلى أبعاد أصغر.[50] فهي تستهلك طاقة أقل بكثير، وتسمح بكثافة أعلى بكثير من الترانزستورات ثنائية القطب.[51] يمكن أن تكون الموسفتات أصغر بكثير من BJTs،[52] أي حوالي واحد على عشرين من الحجم بحلول أوائل التسعينيات.[52] تتمتع الموسفتات أيضاً بسرعة إبدال أعلى،[4] مع تبديل إلكتروني سريع التشغيل والإيقاف مما يجعلها مثالية لتوليد قطار نبضات،[53] أساس الإشارات الرقمية.[54][55] على عكس BJTs، التي تولد ببطء أكثر إشارات تناظرية تشبه الموجات الجيبية،[53] كما أن الترانزستورات الموسفتات أرخص[56] ولها خطوات معالجة بسيطة نسبياً، مما يؤدي إلى ارتفاع إنتاجية التصنيع.[50] وهكذا فإن دوائر الموسفت تتيح الحصول على دائرة متكاملة على نطاق واسع (LSI)، وهي مثالية للدوائر الرقمية،[57]وكذلك الدوائر التناظرية الخطية.[53]

وُصف الموسفت بشكل مختلف على أنه أهم ترانزستور،[3]وأنه أهم عنصر في صناعة الإلكترونيات،[58] ويمكن القول إنه أهم عنصر في صناعة الحوسبة،[59]وأحد أهم التطورات في تكنولوجيا أشباه الموصلات،[60]وربما أهم اختراع في مجال الإلكترونيات.[61] لقد كانت الموسفتات هي اللبنة الأساسية في الإلكترونيات الرقمية الحديثة،[10] during the digital revolution,[62] ثورة المعلومات، عصر المعلومات،[63] وعصر السليكون.[64][65] كانت الموسفتات القوة الدافعة وراء ثورة الحاسب والتقنيات التي مكنتها من ذلك.[66][67][68]كما تم تحقيق التقدم السريع في صناعة الإلكترونيات خلال أواخر القرن العشرين إلى أوائل القرن الحادي والعشرين من خلال تحجيم الموسفتات (مقياس دنار و[[قانون مور])، وصولًا إلى مستوى الإلكترونيات النانوية في أوائل القرن الحادي والعشرين.[69]وقد أحدثت الموسفتات ثورة في العالم خلال عصر المعلومات، مع كثافتها العالية التي مكنت الحاسب من التواجد على عدد قليل من شرائح IC الصغيرة بدلاً من ملء غرفة،[70] ولاحقاً جعل تكنولوجيا الاتصالات الرقمية ممكنة مثل الهواتف الذكية.[66]

الموسفت هو الجهاز أو العنصر الأكثر تصنيعاً في التاريخ.[71][72]كما تحقق الموسفتات مبيعات سنوية تبلغ US$295 billion اعتباراً من عام 2015.[73] بين عامي 1960 و2018، تم تصنيع ما يقدر بنحو 13 sextillion ترانزستور MOS، وهو ما يمثل 99.9٪ على الأقل من جميع الترانزستورات.[71] تحتوي الدوائر الرقمية المتكاملة مثل المعالجات الدقيقة وأجهزة الذاكرة على آلاف إلى مليارات من الموسفتات المتكاملة على كل جهاز، مما يوفر وظائف التبديل الأساسية المطلوبة لتنفيذ بوابة منطقية وتخزين البيانات. هناك أيضاً أجهزة ذاكرة تحتوي على تريليون ترانزستور MOS على الأقل، مثل بطاقة الذاكرة microSD 256 GB، أكبر من عدد النجوم في المجرة درب التبانة.[45] اعتباراً من عام 2010، بقيت مبادئ تشغيل الموسفتات الحديثة إلى حد كبير هي نفسها كما كانت الموسفتات الأصلية التي أظهرها لأول مرة محمد عطا الله وداوون كانگ في عام 1960.[74][75]

يصف مكتب براءات الاختراع والعلامات التجارية الأمريكي الموسفت بأنه "اختراع رائد غيّر الحياة والثقافة حول العالم"[66] وينسب متحف تاريخ الحاسوب إليه الفضل في "تغيير التجربة الإنسانية بشكل لا رجعة فيه".[10] كانت الموسفتات أيضاً أساس جائزة نوبل للأقسام الفائزة مثل تأثير هول الكمي[76] والأجهزة مقرونة الشحنة (CCD)،[77] على الرغم من عدم تسليم أي جائزة نوبل عن الموسفت نفسه.[78] في مذكرة 2018 بشأن جائزة نوبل للفيزياء لجاك كلبي لدوره في اختراع الدائرة المتكاملة، ذكرت الأكاديمية الملكية السويدية للعلوم الموسفت والمعالج الدقيق على وجه التحديد اختراعات أخرى مهمة في تطور الإلكترونيات الدقيقة.[79] كما تم تضمين الوسفت أيضاً في قائمة معالم IEEE في الإلكترونيات،[80] ودخل مخترعاه محمد عطا الله وداوون كانگ القاعة الوطنية لمشاهير المخترعين في عام 2009.[13][14]

التركيب

عادة ما تكون أشباه الموصلات المختارة هي السليكون. في الآونة الأخيرة، بدأت بعض الشركات المصنعة للرقائق، وعلى الأخص آيبيإم وإنتل، في استخدام مركب كيميائي من السليكون والجرمانيوم (SiGe) في قنوات الموسفت. لسوء الحظ، فإن العديد من أشباه الموصلات التي تتمتع بخصائص كهربائية أفضل من السليكون، مثل زرنيخيد الگاليوم، لا تشكل واجهات جيدة من أشباه الموصلات إلى العازل، وبالتالي فهي غير مناسبة للموسفتات. يستمر البحث[when?] حول إنشاء عوازل بخصائص كهربائية مقبولة على مواد أشباه الموصلات الأخرى.

للتغلب على الزيادة في استهلاك الطاقة بسبب تسرب تيار البوابة، يتم استخدام عازل كهربائي عالي بدلاً من ثاني أكسيد السليكون لعازل البوابة، بينما يتم استبدال الپولي سليكون بالبوابات المعدنية (على سبيل المثال إنتل، 2009[81]).

تُفصل البوابة عن القناة بواسطة طبقة عازلة رقيقة، تقليدياً من ثاني أكسيد السليكون وبعد ذلك من أكسيد السليكون. بدأت بعض الشركات في إدخال تركيبة عازلة عالية وبوابة معدنية في العقدة 45 نانومتر.

عندما يتم تطبيق جهد بين البوابة وأطراف البنية، فإن المجال الكهربائي المتولد يخترق الأكسيد ويخلق طبقة الانعكاس أو قناة العبور عند واجهة عازل أشباه الموصلات تجعل هذا الجزء أقل نوعاً ويمهد الطريق لتوصيل التيار مما يؤدي إلى زيادة الجهد بين البوابة والجسم مما يدفع الثقوب ويخلق طبقة من الناقلات الثابتة المشحونة سلباً. كما توفر طبقة الانعكاس قناة يمكن للتيار من خلالها المرور بين طرفي المنبع والمصرف. يؤدي تغيير الجهد بين البوابة والجسم إلى تعديل الموصلية لهذه الطبقة، وبالتالي يتحكم في تدفق التيار بين المصرف والمنبع. يُعرف هذا بوضع التعزيز.

التشغيل

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

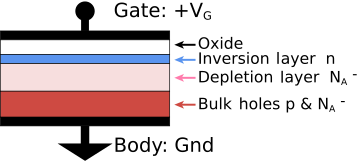

بنية شبه الموصل أكسيد المعدني

يتم الحصول على البنية التقليدية لشبه الموصل أكسيد المعدني (MOS) من خلال تنمية طبقة من ثاني أكسيد السليكون (SiO 2) فوق ركيزة السيليكون، عادةً بواسطة الأكسدة الحرارية وترسيب طبقة من المعدن أو سليكون متعدد البلورات (هذا الأخير شائع الاستخدام). نظراً لأن ثاني أكسيد السيليكون هو مادة عازلة كهربائياً، فإن هيكلها يعادل مستوي مكثف، مع استبدال أحد أقطاب شبه موصل.

عندما يتم تطبيق جهد عبر هيكل MOS، فإنه يعدل توزيع الشحنات في أشباه الموصلات. إذا أخذنا في الاعتبار أشباه الموصلات من النوع p (مع كثافة المتقبلات، p كثافة الثقوب؛ p = NA عن طريق إبعاد الثقوب الموجبة الشحنة بعيداً عن واجهة عازل البوابة/أشباه الموصلات، تاركاً منطقة خالية من الناقل من أيونات مستقبلية سالبة الشحنة غير متحركة (انظر تشويب). إذا كان مرتفعاً بدرجة كافية، يتشكل تركيز عالٍ من ناقلات الشحنة السالبة في الطبقة العاكسة الموجود في طبقة رقيقة بجوار الواجهة بين أشباه الموصلات والعازل.

تقليدياً، يُطلق على جهد البوابة الذي تكون عنده كثافة حجم الإلكترونات في طبقة الانعكاس هي نفسها كثافة حجم الثقوب في الجسم عتبة الجهد. عندما يتجاوز الجهد بين بوابة الترانزستور والمنبع (VGS) عتبة الجهد (Vth)، يُعرف الفرق باسم الجهد الزائد.

هذه البنية ذات البنية من النوع p هي أساس الموسفت من النوع n، والتي تتطلب إضافة مناطق المنبع والمصرف من النوع n.

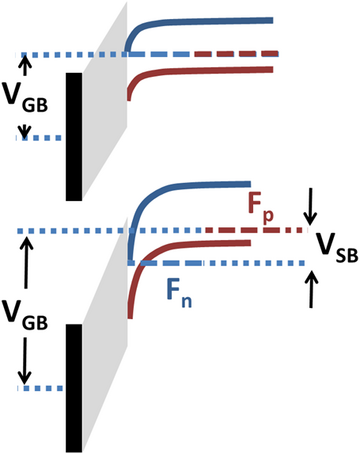

مكثفات MOS ومخططات الحزمة

هيكل مكثف MOS هو قلب الموسفت. لنضع في الاعتبار مكثف MOS حيث تكون قاعدة السليكون من النوع p. إذا تم تطبيق جهد موجب عند البوابة، فسيتم صد الثقوب الموجودة على سطح الركيزة من النوع p بواسطة المجال الكهربائي الناتج عن الجهد المطبق. في البداية، سيتم صد الثقوب ببساطة وما سيبقى على السطح سيكون ذرات ثابتة (سالبة) من النوع المتقبل، مما يخلق منطقة استنفاد على السطح. تذكر أن ثقباً يتم إنشاؤه بواسطة ذرة مستقبل، على سبيل المثال البورون، الذي يحتوي على إلكترون واحد أقل من السليكون. قد يتساءل المرء كيف يمكن صد الثقوب إذا كانت في الواقع غير كيانات؟ الإجابة هي أن ما يحدث حقاً ليس أن الثقب يتم صده، ولكن الإلكترونات تنجذب بواسطة المجال الإيجابي، وتملأ هذه الثقوب، مما يخلق منطقة استنفاد حيث لا توجد حاملات شحنة لأن الإلكترون الآن مثبت على الذرة وغير متحرك.

مع زيادة الجهد عند البوابة، ستكون هناك نقطة يتم فيها تحويل السطح فوق منطقة الاستنزاف من النوع p إلى النوع n، حيث ستبدأ الإلكترونات من المنطقة السائبة في الانجذاب إلى المجال الكهربائي الأكبر. يُعرف هذا باسم "العكس". يعد جهد العتبة الذي يحدث عنده هذا التحويل أحد أهم الپارامترات في الموسفت.

في حالة البنية من النوع p، يحدث الانعكاس عندما يصبح مستوى الطاقة الجوهري على السطح أصغر من مستوى فيرمي على السطح. يمكن للمرء أن يرى هذا من مخطط الحزمة. تذكر أن مستوى فيرمي يحدد نوع أشباه الموصلات قيد المناقشة. إذا كان مستوى فيرمي مساوياً للمستوى الأساسي، فإن أشباه الموصلات تكون من النوع الأساسي أو النقي. إذا كان مستوى فيرمي أقرب إلى نطاق التوصيل (نطاق التكافؤ)، فسيكون نوع أشباه الموصلات من النوع n (النوع p). لذلك، عندما يتم زيادة جهد البوابة بمعنى إيجابي (للمثال المعطى)، فإن هذا "يلوي" نطاق مستوى الطاقة الأساسي بحيث ينحني لأسفل باتجاه نطاق التكافؤ. إذا كان مستوى فيرمي أقرب إلى نطاق التكافؤ (للنوع p)، فستكون هناك نقطة يبدأ فيها المستوى الداخلي في عبور مستوى فيرمي وعندما يصل الجهد إلى عتبة الجهد، فإن المستوى الأساسي لا يتجاوز مستوى فيرمي، وهذا ما يعرف بالانعكاس. عند هذه النقطة، يتم عكس سطح أشباه الموصلات من النوع p إلى النوع n. تذكر أنه كما ذكرنا سابقاً، إذا كان مستوى فيرمي أعلى من المستوى الداخلي، فإن أشباه الموصلات تكون من النوع n، وبالتالي عند الانعكاس، عندما يصل المستوى الداخلي ويتجاوز مستوى فيرمي (الذي يقع أقرب إلى نطاق التكافؤ)، فإن أشباه الموصلات تغييرات الكتابة على السطح كما تمليه المواضع النسبية لمستويات الطاقة الفيرمي والأساسية.

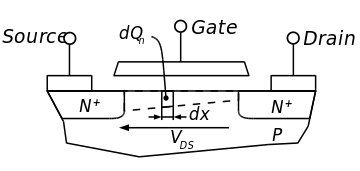

تشكيل الهيكل والقناة

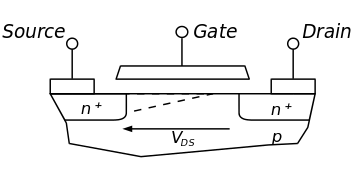

يعتمد ترميز الموسفت على تعديل تركيز الشحنة بواسطة سعة MOS بين هيكل قطب كهربائي وقطب بوابة يقع فوق الهيكل ومعزول عن جميع مناطق الجهاز الأخرى بواسطة طبقة بوابة عازلة للكهرباء. إذا تم استخدام عوازل كهربائية غير أكسيد، فيمكن الإشارة إلى الجهاز على أنه عازل شبه موصل معدني FET (MISFET). مقارنة بمكثف MOS، تشتمل الموسفتات على محطتين إضافيتين (المنبع والمصرف)، كل منهما متصل بمناطق فردية مخدرة للغاية مفصولة بمنطقة الجسم. يمكن أن تكون هذه المناطق إما من النوع p أو n، ولكن يجب أن تكون كلاهما من نفس النوع، ومن النوع المقابل لمنطقة الهيكل. المنبع والمصرف (على عكس الهيكل) المطعم بشكل كبير كما هو موضح بعلامة "+" بعد نوع التطعيم.

إذا كانت الموسفتات عبارة عن قناة n أو nMOS FET، فإن المنبع والمصرف هما مناطق n+ والهيكل عبارة عن منطقة p. إذا كانت الموسفتات عبارة عن قناة p أو pMOS FET، فإن المنبع والمصرف هما مناطق p+ والهيكل عبارة عن منطقة n. سمي المصدر بهذا الاسم لأنه مصدر حاملات الشحنة (إلكترونات القناة n، الثقوب للقناة p) التي تتدفق عبر القناة؛ وبالمثل، فإن المصرف هو المكان الذي تغادر فيه حاملات الشحن القناة.

يتم تحديد شغل نطاقات الطاقة في أشباه الموصلات من خلال موضع مستوى فيرمي بالنسبة لحواف نطاق الطاقة لأشباه الموصلات.

مع جهد البوابة الكافي، يتم دفع حافة نطاق التكافؤ بعيداً عن مستوى فيرمي، ويتم دفع الثقوب من الجسم بعيداً عن البوابة.

عند انحياز أكبر للبوابة، بالقرب من سطح أشباه الموصلات، يتم تقريب حافة نطاق التوصيل من مستوى فيرمي، مما يؤدي إلى ملء السطح بالإلكترونات في طبقة انعكاس أو قناة n في الواجهة بين المنطقة p والأكسيد. وتمتد هذه القناة الموصلة بين المنبع والمصرف، ويتم توصيل التيار من خلالها عند تطبيق جهد بين القطبين. تؤدي زيادة الجهد على البوابة إلى زيادة كثافة الإلكترون في طبقة الانعكاس وبالتالي زيادة تدفق التيار بين المنبع والمصرف. بالنسبة لجهود البوابة التي تقل عن قيمة العتبة، فإن القناة مأهولة بالسكان بشكل خفيف، ويمكن فقط لتيار صغير جداً أن يتدفق بعتبة فرعية أن يتدفق بين المنبع والمصرف.

عندما يتم تطبيق مصدر-جهد بوابة سالب، فإنه يخلق قناة p على سطح المنطقة n، على غرار حالة القناة n، ولكن مع أقطاب متعاكسة من الشحنات والفولتية. عندما يتم تطبيق جهد أقل سالب من قيمة العتبة (جهد سلبي للقناة p) بين البوابة والمصدر، تختفي القناة ويمكن فقط لتيار عتبة فرعي صغير جداً أن يتدفق بين المنبع والمصرف. قد يشتمل الجهاز على جهاز [[Silicon on insulator |سليكون على عازل]] حيث يتكون أكسيد مدفون أسفل طبقة رقيقة من أشباه الموصلات. إذا كانت منطقة القناة بين البوابة العازلة ومنطقة الأكسيد المدفونة رفيعة جداً، يُشار إلى القناة على أنها منطقة قناة فائقة الرقة مع تكوين مناطق المصدر والتصريف على أي جانب في أو فوق طبقة أشباه الموصلات الرقيقة. يمكن استخدام مواد أشباه الموصلات الأخرى. عندما تتشكل مناطق المنبع والمصرف فوق القناة كلياً أو جزئياً، يشار إليها على أنها مناطق منبع/مصرف مثارة.

| الپارامتر | موسفت n | موسفت p | |

|---|---|---|---|

| نوع منبع/مصرف | نوع-n | نوع-p | |

| نوع القناة (مكثف موس) |

نوع-n | نوع-p | |

| نوع البوابة |

پولي سليكون | n+ | p+ |

| المعدن | φm ~ حزمة توصيل السليكون | φm ~ حزمة تكافؤ السليكون | |

| نوع المنبع | نوع-p | نوع-n | |

| جهد العتبة، Vth |

|

| |

| التواء الحزمة | للأسفل | للأعلى | |

| حاملات طبقة الانعكاس | إلكترونات | الثقوب | |

| نوع المادة المتفاعلة | نوع-p | نوع-n | |

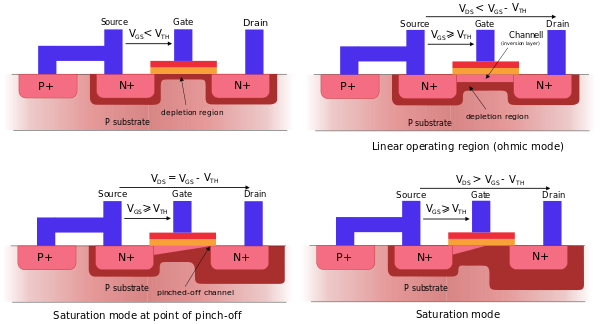

أوضاع العمل

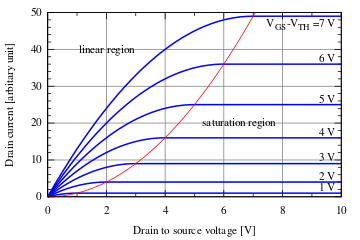

يمكن فصل تشغيل الموسفت إلى ثلاثة أوضاع مختلفة، اعتماداً على الڤولتية في الطرفيات. في المناقشة التالية، تم استخدام نموذج جبري مبسط.[84] تعد خصائص الموسفت الحديثة أكثر تعقيداً من النموذج الجبري المقدم هنا.[85]

بالنسبة لـ وضع التعزيز، للموسفت ذو القناة-n، فإن أوضاع التشغيل الثلاثة هي:

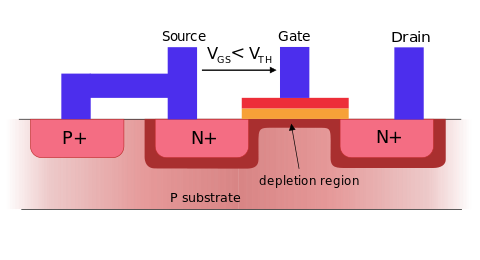

- وضع القطع والعتبة الفرعية والعكس الضعيف (للموسفت ذو القناة-n)

عندما VGS < Vth:

where هو تحيز من بوابة إلى منبع و هي عتبة الجهد للعنصر.

وفقًا لنموذج العتبة الأساسي، يتم إيقاف تشغيل الترانزستور، ولا يوجد توصيل بين المصرف والمنبع. يأخذ النموذج الأكثر دقة في الاعتبار تأثير الطاقة الحرارية على توزيع فيرمي-ديراك لطاقات الإلكترون التي تسمح لبعض الإلكترونات الأكثر نشاطاً عند المنبع بدخول القناة والتدفق إلى المصرف. ينتج عن هذا تيار عتبة فرعي يمثل وظيفة أسية لجهد منبع البوابة. في حين أن التيار بين المصرف والمنبع يجب أن يكون صفراً بشكل مثالي عند استخدام الترانزستور كمفتاح إيقاف، فهناك تيار انعكاس ضعيف، يُسمى أحياناً تسرب العتبة الفرعية. في انعكاس ضعيف حيث يكون المنبع مرتبطاً بكميات كبيرة، يتغير التيار بشكل كبير مع كما هو معطى تقريباً بـ:[86][87]

حيث = التيار عند , الجهد الحراري ويعطى عامل الانحدار n بـ:

تكون =سعة طبقة النضوب و = سعة طبقة الأكسيد. تُستخدم هذه المعادلة بشكل عام، ولكنها مجرد تقريب كافٍ للمنبع المرتبط بالجزء الأكبر. بالنسبة للمنبع غير المرتبط بالجزء الأكبر، فإن معادلة العتبة الفرعية لتيار التصريف في التشبع هي[88][89]

حيث هو مقسم القناة المعطى بـ:

يكون = سعة طبقة النضوب و = سعة طبقة الأكسيد. في العنصر ذي القناة الطويلة، لا يوجد اعتماد على جهد الصرف للتيار مرة واحدة , ولكن مع تقليل طول القناة ينخفض الحاجز الناجم عن التصريف ويقدم اعتماد جهد التصريف الذي يعتمد بطريقة معقدة على هندسة الجهاز (على سبيل المثال، منشطات القناة، تقاطع المنشطات وما إلى ذلك). في كثير من الأحيان، تظهر عتبة الجهد Vth بالنسبة لهذا الوضع، يتم تعريف جهد البوابة الذي يتم عنده تحديد قيمة التيار ID0 على سبيل المثال، ID0 = 1 μA, والتي قد لا تكون هي نفسها Vth-value المستخدمة في المعادلات للأوضاع التالية.

صُممت بعض الدوائر التناظرية ذات الطاقة الصغيرة للاستفادة من توصيل العتبة الفرعية.[90][91][92] من خلال العمل في منطقة الانعكاس الضعيف، توفر الدوائر الموسفت في هذه الدوائر أعلى نسبة ممكنة من الموصلية التحويلية إلى التيار، وهي: , الترانزستور ثنائي القطب.[93]

تعتمد العتبة الفرعية I–V curve بشكل أسي على عتبة الجهد، مما يؤدي إلى اعتماد قوي على أي اختلاف في التصنيع يؤثر على جهد العتبة؛ على سبيل المثال: الاختلافات في سمك الأكسيد، أو عمق الوصلة، أو منشطات الجسم التي تغير درجة خفض الحاجز الناجم عن التصريف. تؤدي الحساسية الناتجة للتغيرات التصنيعية إلى تعقيد تحسين التسرب والأداء.[94][95]

- الوضع الصمام الثلاثي أو المنطقة الخطية، والمعروفة أيضاً باسم الوضع الأومي[96][97] (n-channel MOSFET)

عندما VGS > Vth و VDS < VGS − Vth:

يُشغَّل الترانزستور، ويتم إنشاء قناة تسمح بمرور التيار بين المصرف والمنبع. يعمل الموسفت كمقاوم، يتم التحكم فيه بواسطة جهد البوابة بالنسبة لكل من جهد المنبع والتصريف. يتم نمذجة التيار من المصرف إلى المنبع على النحو التالي:

حيث هي الحامل الفعال للحركة، هو عرض البوابة، هو طول البوابة و هي سعة أكسيد البوابة لكل وحدة مساحة. الانتقال من منطقة العتبة الفرعية الأسية إلى منطقة الصمام الثلاثي ليس حاداً كما توحي المعادلات.

عندما VGS > Vth و VDS ≥ (VGS – Vth):

يُشغَّل المفتاح، وتم إنشاء قناة تسمح بالتيار بين المصرف والمنبع. نظراً لأن جهد المصرف أعلى من جهد المنبع، تنتشر الإلكترونات، ولا يتم التوصيل عبر قناة ضيقة ولكن من خلال توزيع تيار أوسع ثنائي أو ثلاثي الأبعاد يمتد بعيداً عن الواجهة وأعمق في الركيزة. تُعرف بداية هذه المنطقة أيضاً باسم إيقاف الضغط للإشارة إلى عدم وجود منطقة القناة بالقرب من الصرف. على الرغم من أن القناة لا تمد الطول الكامل للجهاز، إلا أن المجال الكهربائي بين المصرف والقناة مرتفع جداً ويستمر التوصيل. يعتمد تيار التصريف الآن بشكل ضعيف على جهد التصريف ويتم التحكم فيه بشكل أساسي بواسطة جهد مصدر البوابة، ويتم تشكيله تقريباً على النحو التالي:

يعمل العامل الإضافي الذي يتضمن λ، پارامتر تعديل طول القناة، على نماذج الاعتماد الحالي على جهد التصريف بسبب تعديل طول القناة، وهو مشابه بشكل فعال لتأثير إرلي الذي يظهر في الأجهزة ثنائية القطب. وفقاً لهذه المعادلة، فإن پارامتر التصميم الرئيسية، تحويل الموسفت هي:

حيث يُطلق على المجموعة Vov = VGS − Vth جهد مضاعف،[100] وحيث VDSsat = VGS − Vth يمثل فجوة بسيطة في والتي قد تظهر بخلاف ذلك عند الانتقال بين منطقتي الصمام الثلاثي والتشبع.

پارامتر تصميم رئيسي آخر هي مقاومة خرج الموسفت المعطى بـ:

- .

rout هو انعكاس gDS حيث . ID هو التعبير في منطقة التشبع.

إذا تم أخذ λ على أنه صفر، فيمكن لمقاومة الخرج اللانهائية الناتجة تبسيط تحليل الدائرة، ولكن هذا قد يؤدي إلى تنبؤات غير واقعية للدائرة، خاصة في الدوائر التناظرية.

عندما يصبح طول القناة قصيراً جداً، تصبح هذه المعادلات غير دقيقة تماماً. تظهر تأثيرات فيزيائية جديدة. على سبيل المثال، قد يصبح نقل الموجة الحاملة في الوضع النشط مقيداً بسرعة التشبع. عندما يهيمن تشبع السرعة، يكون تيار تصريف التشبع خطياً تقريباً أكثر من التربيعي في VGS. بأطوال أقصر، تنقل الحاملات مع تشتت قريب من الصفر، يُعرف باسم شبه - التوصيل البالستي. في النظام البالستي، تتحرك الناقلات بسرعة حقن قد تتجاوز سرعة التشبع وتقترب من سرعة فيرمي بكثافة شحنة انعكاس عالية. بالإضافة إلى ذلك، يؤدي خفض الحاجز الناجم عن التصريف إلى زيادة التيار خارج الحالة (القطع) ويتطلب زيادة في جهد العتبة للتعويض، مما يؤدي بدوره إلى تقليل تيار التشبع.

تأثير الهيكل

يتم تحديد شغل نطاقات الطاقة في أشباه الموصلات من خلال موضع مستوى فيرمي بالنسبة لحواف نطاق الطاقة لأشباه الموصلات. ويقدم تطبيق التحيز العكسي من المنبع إلى الركيزة لتقاطع pn المصدر والجسم انقساماً بين مستويات فيرمي للإلكترونات والثقوب، مما يؤدي إلى تحريك مستوى ميرمي للقناة بعيداً عن حافة النطاق، مما يقلل من شغل القناة. التأثير هو زيادة جهد البوابة اللازم لإنشاء القناة، كما هو موضح في الشكل. هذا التغيير في قوة القناة عن طريق تطبيق التحيز العكسي يسمى "تأثير الهيكل".

ببساطة، باستخدام مثال nMOS، يضع الانحياز من البوابة إلى الهيكل VGB مستويات طاقة نطاق التوصيل، بينما الانحياز من المصدر إلى الجسم VSB يضع مستوى الإلكترون فيرمي بالقرب من الواجهة، ويقرر شغل هذه المستويات بالقرب من الواجهة، وبالتالي قوة الطبقة أو القناة المعكوسة.

يمكن وصف تأثير الجسم على القناة باستخدام تعديل جهد العتبة، تقريباً بالمعادلة التالية:

- VTB=VT0 إذا كان VSB=0 أي تقصير جهد العتبة لأطراف البوابة والهيكل.

حيث VTB هو جهد العتبة مع وجود انحياز الركيزة، وVT0 هي القيمة صفر - VSB من عتبة الجهد، هي پارامتر تأثير الهيكل، و2φB هي انخفاض الجهد التقريبي بين الهيكل والحجم عبر طبقة النضوب عند VSB = 0 وانحياز البوابة كافيان لضمان وجود القناة. بالنسبة للركيزة من النوع p المطعم بشكل موحد مع تطعيم بكميات كبيرة من NA لكل وحدة حجم،

يمكن تشغيل الهيكل كبوابة ثانية، ويشار إليه أحياناً باسم "البوابة الخلفية"؛ يسمى تأثير الهيكل أحياناً "تأثير البوابة الخلفية".[101]

رموز الدارة

| P-channel |

|

|

|

|

|

|---|---|---|---|---|---|

| N-channel |

|

|

|

|

|

| JFET | MOSFET enhancement mode |

MOSFET enhancement mode (no bulk) |

MOSFET depletion mode | ||

يتم استخدام مجموعة متنوعة من رموز الموسفت. التصميم الأساسي هو بشكل عام خط للقناة مع المنبع والمصرف وتركه في زوايا قائمة ثم ينحني للخلف بزوايا قائمة في نفس اتجاه القناة. في بعض الأحيان يتم استخدام ثلاثة مقاطع خطية لـ وضع التعزيز وخط متصل لوضع الاستنفاد (انظر أوضاع الاستنفاد والتعزيز). يتم رسم خط آخر موازٍ لقناة البوابة.

يظهر اتصال الهيكل أو الجسم، إذا تم عرضه، متصلاً بالجزء الخلفي من القناة مع سهم يشير إلى pMOS أو nMOS. تشير الأسهم دائماً من P إلى N، لذا فإن NMOS (قناة N في بئر P أو ركيزة P) لها السهم الذي يشير إلى الداخل (من الجزء الأكبر إلى القناة). إذا كان الجزء الأكبر متصلاً بالمصدر (كما هو الحال عموماً مع الأجهزة المنفصلة)، فإنه يكون مائلاً في بعض الأحيان لمقابلة المصدر الذي يترك الترانزستور. إذا لم يتم عرض الجزء الأكبر (كما هو الحال في كثير من الأحيان في تصميم IC لأنها عبارة عن كتلة شائعة بشكل عام)، يتم استخدام رمز الانعكاس أحياناً للإشارة إلى PMOS، وبدلاً من ذلك، يمكن استخدام سهم على المصدر بنفس طريقة استخدام الترانزستورات ثنائية القطب ( من أجل nMOS، في لـ pMOS).

تتوفر مقارنة بين رموز موسفت في وضع التعزيز ووضع الاستنفاد، جنباً إلى جنب مع رموز JFET، في الجدول في هذا القسم. اتجاه الرموز، وأهمها موضع المنبع بالنسبة للتصريف، هو أن الفولتية الموجبة تظهر أعلى على الصفحة التخطيطية من الفولتية الأقل إيجابية، مما يعني أن التيار يتدفق "لأسفل" الصفحة.[102][103][104]

في المخططات حيث لا يتم تسمية G وS وD، تشير الميزات التفصيلية للرمز إلى أي طرف هو المصدر وأيها استنزاف. بالنسبة إلى رموز الموسفت الخاصة بوضع التعزيز ووضع الاستنفاد (في العمودين الثاني والخامس)، يكون طرف المصدر هو الموصل برأس السهم. بالإضافة إلى ذلك، في هذا الرسم البياني، تظهر البوابة على شكل حرف "L"، حيث يكون ساق الإدخال أقرب إلى S من D، مما يشير أيضاً إلى أيهما. ومع ذلك، غالباً ما يتم رسم هذه الرموز باستخدام بوابة على شكل حرف "T" (كما هو الحال في أي مكان آخر في هذه الصفحة)، لذلك يجب الاعتماد على رأس السهم للإشارة إلى محطة المنبع.

بالنسبة للرموز التي يظهر بها الجزء الأكبر أو الهيكل، المحطة الطرفية، تظهر هنا متصلة داخلياً بالمنبع (أي رأس السهم الأسود في المخططات في العمودين 2 و5). هذا تكوين نموذجي، ولكنه ليس التكوين المهم الوحيد بأي حال من الأحوال. بشكل عام، الموسفت هو عنصر رباعي الأطراف، وفي الدوائر المتكاملة، تشترك العديد من الموسفتات في اتصال الهيكل، وليس بالضرورة أن تكون متصلة بأطراف المصدر لجميع الترانزستورات.

أنواع الموسفتات

منطق PMOS و NMOS

يستخدم P-channel MOS (PMOS) logic الموسفتات ذات القناة P لتنفيذ البوبات المنطقية والدوائر الرقمية الأخرى. يستخدم N-channel MOS (NMOS) logic موسفتات ذات القناة n لتنفيذ البوابات المنطقية والدوائر الرقمية الأخرى.

بالنسبة للأجهزة ذات القدرة المتساوية على القيادة الحالية، يمكن جعل دوائر الموسفت ذات القنوات n أصغر من دوائر الموسفت ذات القناة p، بسبب ناقلات الشحنة ذات القناة p ( الثقوب) ذات حركية أقل من حاملات الشحنة n-channel (الإلكترونات)، وإنتاج نوع واحد فقط من الموسفتات على ركيزة من السيليكون أرخص وأبسط من الناحية الفنية. كانت هذه هي المبادئ الدافعة في تصميم منطق NMOS الذي يستخدم الموسفتات ذات القناة n حصرياً. ومع ذلك، على عكس منطق CMOS (إهمال تسرب التيار)، يستهلك منطق NMOS الطاقة حتى في حالة عدم حدوث تبديل.

قام محمد محمد عطا الله وداوون كانگ في الأصل بعرض كل من أجهزة pMOS وnMOS بطول بوابة 20 µm ثم 10 µm في عام 1960.[15][105]لدى أجهزة الموسفت الأصلية أيضاً سمك أكسيد البوابة 100 nm.[106] ومع ذلك، كانت أجهزة nMOS غير عملية، وكان نوع pMOS فقط أجهزة عمل عملية.[15] تم تطوير عملية NMOS أكثر عملية بعد عدة سنوات. كان NMOS في البداية أسرع من CMOS، وبالتالي استُخدم NMOS على نطاق واسع لأجهزة الحاسب في السبعينيات.[107] مع التقدم التكنولوجي، حل منطق CMOS محل منطق NMOS في منتصف الثمانينيات ليصبح العملية المفضلة للرقائق الرقمية.

أشباه الموصلات ذات الأكاسيد المعدنية المُتتامة (سيموس)

يتم استخدام الموسفت في المنطق الرقمي لأشباه الموصلات ذات الأكاسيد المعدنية المُتتامة (CMOS)،[108]التي تستخدم دوائر موسفت ذات القناة p وn ككتل بناء. السخونة الزائدة هي مصدر قلق كبير في الدوائر المتكاملة منذ أن تم تعبئة المزيد من الترانزستورات في رقائق أصغر من أي وقت مضى. يقلل منطق سيموس من استهلاك الطاقة لأنه لا يوجد تدفق للتيار (بشكل مثالي)، وبالتالي لا يتم استهلاك القدرة، إلا عند تبديل مدخلات البوابات المنطقية. يحقق منطق سيموس هذا التخفيض الحالي من خلال استكمال كل nMOSFET مع pMOSFET وربط كل من البوابات والمصارف معاً. سيؤدي الجهد العالي على البوابات إلى إجراء nMOSFET وعدم إجراء pMOSFET والجهد المنخفض على البوابات يؤدي إلى عكس ذلك. أثناء وقت التبديل حيث ينتقل الجهد من حالة إلى أخرى، سيعمل كلا الموسفت لفترة وجيزة. يقلل هذا الترتيب بشكل كبير من استهلاك الطاقة وتوليد الحرارة.

طُورت سيموس بواسطة تشيه-تانگ ساه وفرانك وانلاس في فيرتشايلد لأشباه الموصلات في عام 1963.[32] كان استهلاك سيموس منخفضاً للطاقة، ولكنه كان أبطأ في البداية من NMOS، والذي كان يستخدم على نطاق واسع لأجهزة الحاسب في السبعينيات. في عام 1978، قدمت هيتاتشي عملية CMOS مزدوجة جيداً، والتي سمحت لسيموس بمطابقة أداء NMOS مع استهلاك أقل للطاقة. تفوقت عملية CMOS ثنائية الازواجية في النهاية على NMOS باعتباره أكثر عملية تصنيع أشباه الموصلات شيوعاً لأجهزة الحاسب في الثمانينيات.[107]بحلول السبعينيات – الثمانينيات، استهلك منطق CMOS أكثر من 7 مرة أقل من منطق NMOS،[107] وحوالي 100000 مرة أقل من منطق ترانزستور-ترانزستور (TTL) ثنائي القطب.[109]

وضع النضوب

هناك أجهزة موسفت وضع النضوب الاستنزاف، وهي أقل استخداماً من أجهزة وضع التعزيز القياسية التي تم وصفها بالفعل. هذه هي أجهزة موسفت مشابة بحيث توجد قناة حتى مع وجود جهد صفري من بوابة إلى منبع. للتحكم في القناة، يتم تطبيق جهد سلبي على البوابة (لجهاز n-channel)، مما يؤدي إلى استنزاف القناة، مما يقلل من تدفق التيار عبر الجهاز. من حيث الجوهر، يكون جهاز وضع النضوب مكافئاً لمفتاح مغلق عادةً (تشغيل)، بينما جهاز وضع التحسين مكافئ لمفتاح مفتوح عادةً (إيقاف).[110]

نظراً لانخفاض عامل الضجيج في منطقة RF، و كسب أفضل، غالباً ما تُفضل هذه الأجهزة على ثنائيات الأقطاب في الواجهات الأمامية للتردد اللاسلكي مثل أجهزة التلفزيون.

تتضمن عائلات موسفت في وضع النضوب BF960 بواسطة سيمنز و تيليفوكن، وBF980 في الثمانينيات بواسطة فيليپس (أصبحت لاحقاً NXP Semiconductors)، والتي لا تزال مشتقاتها تستخدم في AGC و مازج الواجهات الأمامية.

ترانزستور الأثر الحقلي للعوازل المعدنية لأشباه الموصلات (ميسفت)

ترانزستور الأثر الحقلي للعوازل المعدنية لأشباه الموصلات،[111][112][113] أو ميسفت، مصطلح أكثر عمومية من موسفت ومرادف لـ ترانزستور الأثر الحقلي معزول البوابة (IGFET). جميع الموسفتات هي ميسفتات، ولكن ليست كل الميسفتات هي موسفتات.

عازل البوابة في المسيفت هو ثاني أكسيد السليكون في الموسفت، ولكن يمكن أيضاً استخدام مواد أخرى. يقع عازل البوابة مباشرة أسفل إلكترود البوابة وفوق القناة في ميسفت. يُستخدم مصطلح معدن تاريخياً للإشارة إلى مادة البوابة، على الرغم من أنها الآن عادةً مشابة بدرجة عالية بپوليسيليكون أو مادة أخرى غير معدنية.

قد تكون أنواع العازل:

- ثاني أكسيد السيليكون، في الترانزستورات

- العوازل العضوية (على سبيل المثال، ترانزستور غير مشاب-پولي أستيلين؛ سيانو إيثيل پولولان، CEP[114])، لترانزستورات الأثر الحقلي ذات الأساس العضوي.[113]

الموسفت ذو البوابة المتحركة (FGMOS)

الموسفت ذو البوابة المتحركة (FGMOS) هو نوع من الموسفات حيث تكون البوابة معزولة، مما يؤدي إلى إنشاء نقطة لقاء متحركة في التيار المستمر ويتم ترسيب عدد من البوابات أو المدخلات الثانوية فوق البوابة العائمة (FG) وهي معزولة كهربياً عنه. تم إعداد التقرير الأول عن الموسفت ذو البوابة المتحركة (FGMOS) بواسطة داوون كانگ (أحد مخترعي موسفت الأصلي) وسيمون مين شي في عام 1967.[115]

يشيع استخدام FGMOS كخلية ذاكرة ببوابة متحركة، وعنصر تخزين رقمي في EPROM وEEPROM و الذاكرة الوميضية. تشمل الاستخدامات الأخرى لـ FGMOS عنصراً حسابياً عصبونياً في الشبكات العصبونية، وعنصر التخزين التناظري، ومقياس الجهد الرقمي و DACs أحادي الترانزستور.

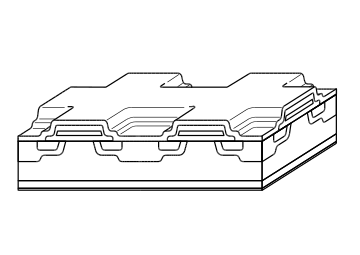

موسفتات القدرة (الموسفتات الاستطاعة)

لموسفتات القدرة بنية مختلفة[116]كما هو الحال مع معظم أجهزة الطاقة، يكون الهيكل عمودياً وليس مستوياً. باستخدام الهيكل الرأسي، من الممكن أن يحافظ الترانزستور على الجهد الكهربي العالي والتيار العالي. تصنيف الجهد للترانزستور هو تابع للإشابات وسمك الطبقة طبقة التنضيد-N (انظر المقطع العرضي)، في حين أن التصنيف الحالي هو تابع لعرض القناة (كلما اتسعت القناة، ارتفع التيار). في البنية المستوية، تعتبر تصنيفات الجهد الحالي والانهيار على حد سواء دالة لأبعاد القناة (عرض وطول القناة على التوالي)، مما يؤدي إلى استخدام غير فعال لـ "وضع السيليكون". مع الهيكل الرأسي، تتناسب منطقة المكون تقريباً مع التيار الذي يمكن أن تتحمله، ويتناسب سمك المكون (في الواقع سمك الطبقة الفوقية (التنضيد) N) مع جهد الانهيار.[117]

تُستخدم موسفتات القدرة ذات الهيكل الجانبي بشكل أساسي في مكبرات الصوت المتطورة وأنظمة PA عالية الطاقة. ميزتها هي سلوك أفضل في المنطقة المشبعة (المقابلة للمنطقة الخطية من ترانزستور ثنائي القطب) من الدوائر المتكاملة منخفضة المقاومة (موسفت) الرأسية. تم تصميم وحدات الموسفت العمودية لتبديل الاستخدامات.[118]

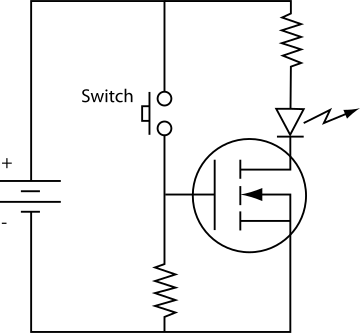

طُورت موسفتات الطاقة، التي يشيع استخدامها في إلكترونيات القدرة، في أوائل السبعينيات.[119] تتيح موسفتات الطاقة طاقة محرك منخفضة للبوابة، وسرعة تحويل سريعة، وقدرة محاذاة متقدمة.[4]

أشباه موصلات أكاسيد المعدن المزدوج التوزيع (DMOS)

هناك VDMOS (أشباه موصلات أكاسيد المعدن المزدوج التوزيع عمودياً) وLDMOS (أشباه موصلات أكاسيد المعدن المزدوج التوزيع جانبياً). يتم تصنيع معظم دوائر الموسفت الكهربائية باستخدام هذه التقنية.

مكثف الموسفت

مكثف الموسفت هو جزء من هيكل الموسفت، حيث يكون مكثف الموسفت محاطاً بوصلتي موجب سالب.[120] يستخدم مكثف الموسفت على نطاق واسع كمكثف تخزين في شريحة ذاكرة، وكحجر بناء أساسي لجهاز مقرون الشحنة (CCD) في تقنية حساس الصورة.[121] في DRAM (ذاكرة الوصول العشوائي) الديناميكية، تتكون كل خلية ذاكرة عادةً من مكثف موسفت و MOS.[122]

Thin-film transistor (TFT)

The thin-film transistor (TFT) is a type of MOSFET distinct from the standard bulk MOSFET.[123] The first TFT was invented by Paul K. Weimer at RCA in 1962, building on the earlier work of Atalla and Kahng on MOSFETs.[124]

The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968.[125] Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated the concept in 1968 with an 18x2 matrix dynamic scattering LCD that used standard discrete MOSFETs, as TFT performance was not adequate at the time.[126]

Bipolar–MOS transistors

BiCMOS is an integrated circuit that combines BJT and CMOS transistors on a single chip.[127]

The insulated-gate bipolar transistor (IGBT) is a power transistor with characteristics of both a MOSFET and bipolar junction transistor (BJT).[128]

MOS sensors

A number of MOSFET sensors have been developed, for measuring physical, chemical, biological and environmental parameters.[129] The earliest MOSFET sensors include the open-gate FET (OGFET) introduced by Johannessen in 1970,[129] the ion-sensitive field-effect transistor (ISFET) invented by Piet Bergveld in 1970,[130] the adsorption FET (ADFET) patented by P.F. Cox in 1974, and a hydrogen-sensitive MOSFET demonstrated by I. Lundstrom, M.S. Shivaraman, C.S. Svenson and L. Lundkvist in 1975.[129] The ISFET is a special type of MOSFET with a gate at a certain distance,[129] and where the metal gate is replaced by an ion-sensitive membrane, electrolyte solution and reference electrode.[131]

By the mid-1980s, numerous other MOSFET sensors had been developed, including the gas sensor FET (GASFET), surface accessible FET (SAFET), charge flow transistor (CFT), pressure sensor FET (PRESSFET), chemical field-effect transistor (ChemFET), reference ISFET (REFET), biosensor FET (BioFET), enzyme-modified FET (ENFET) and immunologically modified FET (IMFET).[129] By the early 2000s, BioFET types such as the DNA field-effect transistor (DNAFET), gene-modified FET (GenFET) and cell-potential BioFET (CPFET) had been developed.[131]

The two main types of image sensors used in digital imaging technology are the charge-coupled device (CCD) and the active-pixel sensor (CMOS sensor). Both CCD and CMOS sensors are based on MOS technology, with the CCD based on MOS capacitors and the CMOS sensor based on MOS transistors.[77]

Multi-gate field-effect transistor (MuGFET)

The dual-gate MOSFET (DGMOS) has a tetrode configuration, where both gates control the current in the device. It is commonly used for small-signal devices in radio frequency applications where biasing the drain-side gate at constant potential reduces the gain loss caused by Miller effect, replacing two separate transistors in cascode configuration. Other common uses in RF circuits include gain control and mixing (frequency conversion). The tetrode description, though accurate, does not replicate the vacuum-tube tetrode. Vacuum-tube tetrodes, using a screen grid, exhibit much lower grid-plate capacitance and much higher output impedance and voltage gains than triode vacuum tubes. These improvements are commonly an order of magnitude (10 times) or considerably more. Tetrode transistors (whether bipolar junction or field-effect) do not exhibit improvements of such a great degree.

The FinFET is a double-gate silicon-on-insulator device, one of a number of geometries being introduced to mitigate the effects of short channels and reduce drain-induced barrier lowering. The fin refers to the narrow channel between source and drain. A thin insulating oxide layer on either side of the fin separates it from the gate. SOI FinFETs with a thick oxide on top of the fin are called double-gate and those with a thin oxide on top as well as on the sides are called triple-gate FinFETs.[132][133]

A double-gate MOSFET transistor was first demonstrated in 1984 by Electrotechnical Laboratory researchers Toshihiro Sekigawa and Yutaka Hayashi.[134][135] A GAAFET (gate-all-around MOSFET), a type of multi-gate non-planar 3D transistor, was first demonstrated in 1988 by a Toshiba research team including Fujio Masuoka, H. Takato and K. Sunouchi.[136][137] The FinFET (fin field-effect transistor), a type of 3D non-planar double-gate MOSFET, originated from the research of Digh Hisamoto and his team at Hitachi Central Research Laboratory in 1989.[138][139] The development of nanowire multi-gate MOSFETs have since become fundamental to nanoelectronics.[140]

Quantum field-effect transistor (QFET)

A quantum field-effect transistor (QFET) or quantum well field-effect transistor (QWFET) is a type of MOSFET[141][142][143] that takes advantage of quantum tunneling to greatly increase the speed of transistor operation.[144]

Radiation-hardened-by-design (RHBD)

Semiconductor sub-micrometer and nanometer electronic circuits are the primary concern for operating within the normal tolerance in harsh radiation environments like outer space. One of the design approaches for making a radiation-hardened-by-design (RHBD) device is enclosed-layout-transistor (ELT). Normally, the gate of the MOSFET surrounds the drain, which is placed in the center of the ELT. The source of the MOSFET surrounds the gate. Another RHBD MOSFET is called H-Gate. Both of these transistors have very low leakage current with respect to radiation. However, they are large in size and take more space on silicon than a standard MOSFET. In older STI (shallow trench isolation) designs, radiation strikes near the silicon oxide region cause the channel inversion at the corners of the standard MOSFET due to accumulation of radiation induced trapped charges. If the charges are large enough, the accumulated charges affect STI surface edges along the channel near the channel interface (gate) of the standard MOSFET. Thus the device channel inversion occurs along the channel edges and the device creates an off-state leakage path, causing the device to turn on. So the reliability of circuits degrades severely. The ELT offers many advantages. These advantages include improvement of reliability by reducing unwanted surface inversion at the gate edges that occurs in the standard MOSFET. Since the gate edges are enclosed in ELT, there is no gate oxide edge (STI at gate interface), and thus the transistor off-state leakage is reduced considerably. Low-power microelectronic circuits including computers, communication devices and monitoring systems in the space shuttle and satellites are very different to what is used on earth. They require radiation (high-speed atomic particles like proton and neutron, solar flare magnetic energy dissipation in Earth's space, energetic cosmic rays like X-ray, gamma ray etc.) tolerant circuits. These special electronics are designed by applying different techniques using RHBD MOSFETs to ensure safer journeys and space-walks for astronauts.

Applications

The MOSFET generally forms the basis of modern electronics,[42] as the dominant transistor in digital circuits as well as analog integrated circuits.[3] It is the basis for numerous modern technologies,[145] and is commonly used for a wide range of applications.[47] According to Jean-Pierre Colinge, numerous modern technologies would not exist without the MOSFET, such as the modern computer industry, digital telecommunication systems, video games, pocket calculators, and digital wristwatches, for example.[145]

Discrete MOSFET devices are widely used in applications such as switch mode power supplies, variable-frequency drives and other power electronics applications where each device may be switching thousands of watts. Radio-frequency amplifiers up to the UHF spectrum use MOSFET transistors as analog signal and power amplifiers. Radio systems also use MOSFETs as oscillators, or mixers to convert frequencies. MOSFET devices are also applied in audio-frequency power amplifiers for public address systems, sound reinforcement and home and automobile sound systems.[بحاجة لمصدر]

MOSFETs in integrated circuits are the primary elements of computer processors, semiconductor memory, image sensors, and most other types of integrated circuits.

MOS integrated circuit (MOS IC)

The MOSFET is the most widely used type of transistor and the most critical device component in integrated circuit (IC) chips.[146] The monolithic integrated circuit chip was enabled by the surface passivation process, which electrically stabilized silicon surfaces via thermal oxidation, making it possible to fabricate monolithic integrated circuit chips using silicon. The surface passivation process was developed by Mohamed M. Atalla at Bell Labs in 1957. This was the basis for the planar process, developed by Jean Hoerni at Fairchild Semiconductor in early 1959, which was critical to the invention of the monolithic integrated circuit chip by Robert Noyce later in 1959.[147][148][17] The same year,[8] Atalla used his surface passivation process to invent the MOSFET with Dawon Kahng at Bell Labs.[14][13] This was followed by the development of clean rooms to reduce contamination to levels never before thought necessary, and coincided with the development of photolithography[149] which, along with surface passivation and the planar process, allowed circuits to be made in few steps.

Mohamed Atalla first proposed the concept of the MOS integrated circuit (MOS IC) chip in 1960, noting that the MOSFET's ease of fabrication made it useful for integrated circuits.[9] In contrast to bipolar transistors which required a number of steps for the p–n junction isolation of transistors on a chip, MOSFETs required no such steps but could be easily isolated from each other.[29] Its advantage for integrated circuits was re-iterated by Dawon Kahng in 1961.[21] The Si–SiO2 system possessed the technical attractions of low cost of production (on a per circuit basis) and ease of integration. These two factors, along with its rapidly scaling miniaturization and low energy consumption, led to the MOSFET becoming the most widely used type of transistor in IC chips.

The earliest experimental MOS IC to be demonstrated was a 16-transistor chip built by Fred Heiman and Steven Hofstein at RCA in 1962.[56] General Microelectronics later introduced the first commercial MOS integrated circuits in 1964, consisting of 120 p-channel transistors.[150] It was a 20-bit shift register, developed by Robert Norman[56] and Frank Wanlass.[151] In 1968, Fairchild Semiconductor researchers Federico Faggin and Tom Klein developed the first silicon-gate MOS IC.[35]

MOS large-scale integration (MOS LSI)

With its high scalability,[48] and much lower power consumption and higher density than bipolar junction transistors,[51] the MOSFET made it possible to build high-density IC chips.[1] By 1964, MOS chips had reached higher transistor density and lower manufacturing costs than bipolar chips. MOS chips further increased in complexity at a rate predicted by Moore's law, leading to large-scale integration (LSI) with hundreds of MOSFETs on a chip by the late 1960s.[152] MOS technology enabled the integration of more than 10,000 transistors on a single LSI chip by the early 1970s,[153] before later enabling very large-scale integration (VLSI).[50][154]

Microprocessors

The MOSFET is the basis of every microprocessor,[45] and was responsible for the invention of the microprocessor.[155] The origins of both the microprocessor and the microcontroller can be traced back to the invention and development of MOS technology. The application of MOS LSI chips to computing was the basis for the first microprocessors, as engineers began recognizing that a complete computer processor could be contained on a single MOS LSI chip.[152]

The earliest microprocessors were all MOS chips, built with MOS LSI circuits. The first multi-chip microprocessors, the Four-Phase Systems AL1 in 1969 and the Garrett AiResearch MP944 in 1970, were developed with multiple MOS LSI chips. The first commercial single-chip microprocessor, the Intel 4004, was developed by Federico Faggin, using his silicon-gate MOS IC technology, with Intel engineers Marcian Hoff and Stan Mazor, and Busicom engineer Masatoshi Shima.[156] With the arrival of CMOS microprocessors in 1975, the term "MOS microprocessors" began to refer to chips fabricated entirely from PMOS logic or fabricated entirely from NMOS logic, contrasted with "CMOS microprocessors" and "bipolar bit-slice processors".[157]

CMOS circuits

Digital

The growth of digital technologies like the microprocessor has provided the motivation to advance MOSFET technology faster than any other type of silicon-based transistor.[158] A big advantage of MOSFETs for digital switching is that the oxide layer between the gate and the channel prevents DC current from flowing through the gate, further reducing power consumption and giving a very large input impedance. The insulating oxide between the gate and channel effectively isolates a MOSFET in one logic stage from earlier and later stages, which allows a single MOSFET output to drive a considerable number of MOSFET inputs. Bipolar transistor-based logic (such as TTL) does not have such a high fanout capacity. This isolation also makes it easier for the designers to ignore to some extent loading effects between logic stages independently. That extent is defined by the operating frequency: as frequencies increase, the input impedance of the MOSFETs decreases.

Analog

The MOSFET's advantages in digital circuits do not translate into supremacy in all analog circuits. The two types of circuit draw upon different features of transistor behavior. Digital circuits switch, spending most of their time either fully on or fully off. The transition from one to the other is only of concern with regards to speed and charge required. Analog circuits depend on operation in the transition region where small changes to Vgs can modulate the output (drain) current. The JFET and bipolar junction transistor (BJT) are preferred for accurate matching (of adjacent devices in integrated circuits), higher transconductance and certain temperature characteristics which simplify keeping performance predictable as circuit temperature varies.

Nevertheless, MOSFETs are widely used in many types of analog circuits because of their own advantages (zero gate current, high and adjustable output impedance and improved robustness vs. BJTs which can be permanently degraded by even lightly breaking down the emitter-base).[vague] The characteristics and performance of many analog circuits can be scaled up or down by changing the sizes (length and width) of the MOSFETs used. By comparison, in bipolar transistors the size of the device does not significantly affect its performance.[بحاجة لمصدر] MOSFETs' ideal characteristics regarding gate current (zero) and drain-source offset voltage (zero) also make them nearly ideal switch elements, and also make switched capacitor analog circuits practical. In their linear region, MOSFETs can be used as precision resistors, which can have a much higher controlled resistance than BJTs. In high power circuits, MOSFETs sometimes have the advantage of not suffering from thermal runaway as BJTs do.[محل شك] Also, MOSFETs can be configured to perform as capacitors and gyrator circuits which allow op-amps made from them to appear as inductors, thereby allowing all of the normal analog devices on a chip (except for diodes, which can be made smaller than a MOSFET anyway) to be built entirely out of MOSFETs. This means that complete analog circuits can be made on a silicon chip in a much smaller space and with simpler fabrication techniques. MOSFETS are ideally suited to switch inductive loads because of tolerance to inductive kickback.

Some ICs combine analog and digital MOSFET circuitry on a single mixed-signal integrated circuit, making the needed board space even smaller. This creates a need to isolate the analog circuits from the digital circuits on a chip level, leading to the use of isolation rings and silicon on insulator (SOI). Since MOSFETs require more space to handle a given amount of power than a BJT, fabrication processes can incorporate BJTs and MOSFETs into a single device. Mixed-transistor devices are called bi-FETs (bipolar FETs) if they contain just one BJT-FET and BiCMOS (bipolar-CMOS) if they contain complementary BJT-FETs. Such devices have the advantages of both insulated gates and higher current density.

In the late 1980s, Asad Abidi pioneered RF CMOS technology, which uses MOS VLSI circuits, while working at UCLA. This changed the way in which RF circuits were designed, away from discrete bipolar transistors and towards CMOS integrated circuits. As of 2008, the radio transceivers in all wireless networking devices and modern mobile phones are mass-produced as RF CMOS devices. RF CMOS is also used in nearly all modern Bluetooth and wireless LAN (WLAN) devices.[159]

MOS memory

The advent of the MOSFET enabled the practical use of MOS transistors as memory cell storage elements, a function previously served by magnetic cores in computer memory.[160] The first modern computer memory was introduced in 1965, when John Schmidt at Fairchild Semiconductor designed the first MOS semiconductor memory, a 64-bit MOS SRAM (static random-access memory).[161] SRAM became an alternative to magnetic-core memory, but required six MOS transistors for each bit of data.[162]

MOS technology is the basis for DRAM (dynamic random-access memory). In 1966, Dr. Robert H. Dennard at the IBM Thomas J. Watson Research Center was working on MOS memory. While examining the characteristics of MOS technology, he found it was capable of building capacitors, and that storing a charge or no charge on the MOS capacitor could represent the 1 and 0 of a bit, while the MOS transistor could control writing the charge to the capacitor. This led to his development of a single-transistor DRAM memory cell.[162] In 1967, Dennard filed a patent under IBM for a single-transistor DRAM (dynamic random-access memory) memory cell, based on MOS technology.[163] MOS memory enabled higher performance, was cheaper, and consumed less power, than magnetic-core memory, leading to MOS memory overtaking magnetic core memory as the dominant computer memory technology by the early 1970s.[164]

Frank Wanlass, while studying MOSFET structures in 1963, noted the movement of charge through oxide onto a gate. While he did not pursue it, this idea would later become the basis for EPROM (erasable programmable read-only memory) technology.[165] In 1967, Dawon Kahng and Simon Min Sze proposed that floating-gate memory cells, consisting of floating-gate MOSFETs (FGMOS), could be used to produce reprogrammable ROM (read-only memory).[166] Floating-gate memory cells later became the basis for non-volatile memory (NVM) technologies including EPROM, EEPROM (electrically erasable programmable ROM) and flash memory.[167]

Consumer electronics

MOSFETs are widely used in consumer electronics. One of the earliest influential consumer electronic products enabled by MOS LSI circuits was the electronic pocket calculator,[153] as MOS LSI technology enabled large amounts of computational capability in small packages.[168] In 1965, the Victor 3900 desktop calculator was the first MOS calculator, with 29 MOS chips.[169] In 1967, the Texas Instruments Cal-Tech was the first prototype electronic handheld calculator, with three MOS LSI chips, and it was later released as the Canon Pocketronic in 1970.[170] The Sharp QT-8D desktop calculator was the first mass-produced LSI MOS calculator in 1969,[171] and the Sharp EL-8 which used four MOS LSI chips was the first commercial electronic handheld calculator in 1970.[170] The first true electronic pocket calculator was the Busicom LE-120A HANDY LE, which used a single MOS LSI calculator-on-a-chip from Mostek, and was released in 1971.[170] By 1972, MOS LSI circuits were commercialized for numerous other applications.[172]

MOSFETs are fundamental to information and communications technology (ICT),[66][79] including modern computers,[173][145][154] modern computing,[174] telecommunications, the communications infrastructure,[173][175] the Internet,[173][72][176] digital telephony,[177] wireless telecommunications,[178][179] and mobile networks.[179] According to Colinge, the modern computer industry and digital telecommunication systems would not exist without the MOSFET.[145] Advances in MOS technology has been the most important contributing factor in the rapid rise of network bandwidth in telecommunication networks, with bandwidth doubling every 18 months, from bits per second to terabits per second (Edholm's law).[180]

MOS sensors

MOS sensors, also known as MOSFET sensors, are widely used to measure physical, chemical, biological and environmental parameters.[129] The ion-sensitive field-effect transistor (ISFET), for example, is widely used in biomedical applications.[131] MOS chemiresistors and MOSFETs have also been extensively shown to have promising applications is gas sensing either as single sensor devices or as components in chemical sensor arrays.[181]

MOSFETs are also widely used in microelectromechanical systems (MEMS), as silicon MOSFETs could interact and communicate with the surroundings and process things such as chemicals, motions and light.[182] An early example of a MEMS device is the resonant-gate transistor, an adaptation of the MOSFET, developed by Harvey C. Nathanson in 1965.[183]

MOS technology is the basis for modern image sensors, including the charge-coupled device (CCD) and the CMOS active-pixel sensor (CMOS sensor), used in digital imaging and digital cameras.[77] Willard Boyle and George E. Smith developed the CCD in 1969. While researching the MOS process, they realized that an electric charge was the analogy of the magnetic bubble and that it could be stored on a tiny MOS capacitor. As it was fairly straightforward to fabricate a series of MOS capacitors in a row, they connected a suitable voltage to them so that the charge could be stepped along from one to the next.[77] The CCD is a semiconductor circuit that was later used in the first digital video cameras for television broadcasting.[184]

The MOS active-pixel sensor (APS) was developed by Tsutomu Nakamura at Olympus in 1985.[185] The CMOS active-pixel sensor was later developed by Eric Fossum and his team at NASA's Jet Propulsion Laboratory in the early 1990s.[186]

MOS image sensors are widely used in optical mouse technology. The first optical mouse, invented by Richard F. Lyon at Xerox in 1980, used a 5 µm NMOS sensor chip.[187][188] Since the first commercial optical mouse, the IntelliMouse introduced in 1999, most optical mouse devices use CMOS sensors.[189]

Power MOSFETs

The power MOSFET is the most widely used power device in the world.[4] Advantages over bipolar junction transistors in power electronics include MOSFETs not requiring a continuous flow of drive current to remain in the ON state, offering higher switching speeds, lower switching power losses, lower on-resistances, and reduced susceptibility to thermal runaway.[190] The power MOSFET had an impact on power supplies, enabling higher operating frequencies, size and weight reduction, and increased volume production.[191]

Switching power supplies are the most common applications for power MOSFETs.[53] They are also widely used for MOS RF power amplifiers, which enabled the transition of mobile networks from analog to digital in the 1990s. This led to the wide proliferation of wireless mobile networks, which revolutionised telecommunication systems.[178] The LDMOS in particular is the most widely used power amplifier in mobile networks, such as 2G, 3G,[178] 4G, and 5G.[179] Over 50 billion discrete power MOSFETs are shipped annually, as of 2018. They are widely used for automotive, industrial and communications systems in particular.[192] Power MOSFETs are commonly used in automotive electronics, particularly as switching devices in electronic control units,[193] and as power converters in modern electric vehicles.[194] The insulated-gate bipolar transistor (IGBT), a hybrid MOS-bipolar transistor, is also used for a wide variety of applications.[195]

Construction

Gate material

The primary criterion for the gate material is that it is a good conductor. Highly doped polycrystalline silicon is an acceptable but certainly not ideal conductor, and also suffers from some more technical deficiencies in its role as the standard gate material. Nevertheless, there are several reasons favoring use of polysilicon:

- The threshold voltage (and consequently the drain to source on-current) is modified by the work function difference between the gate material and channel material. Because polysilicon is a semiconductor, its work function can be modulated by adjusting the type and level of doping. Furthermore, because polysilicon has the same bandgap as the underlying silicon channel, it is quite straightforward to tune the work function to achieve low threshold voltages for both NMOS and PMOS devices. By contrast, the work functions of metals are not easily modulated, so tuning the work function to obtain low threshold voltages (LVT) becomes a significant challenge. Additionally, obtaining low-threshold devices on both PMOS and NMOS devices sometimes requires the use of different metals for each device type. While bimetallic integrated circuits (i.e., one type of metal for gate electrodes of NFETS and a second type of metal for gate electrodes of PFETS) are not common, they are known in patent literature and provide some benefit in terms of tuning electrical circuits' overall electrical performance.

- The silicon-SiO2 interface has been well studied and is known to have relatively few defects. By contrast many metal-insulator interfaces contain significant levels of defects which can lead to Fermi level pinning, charging, or other phenomena that ultimately degrade device performance.

- In the MOSFET IC fabrication process, it is preferable to deposit the gate material prior to certain high-temperature steps in order to make better-performing transistors. Such high temperature steps would melt some metals, limiting the types of metal that can be used in a metal-gate-based process.

While polysilicon gates have been the de facto standard for the last twenty years, they do have some disadvantages which have led to their likely future replacement by metal gates. These disadvantages include:

- Polysilicon is not a great conductor (approximately 1000 times more resistive than metals) which reduces the signal propagation speed through the material. The resistivity can be lowered by increasing the level of doping, but even highly doped polysilicon is not as conductive as most metals. To improve conductivity further, sometimes a high-temperature metal such as tungsten, titanium, cobalt, and more recently nickel is alloyed with the top layers of the polysilicon. Such a blended material is called silicide. The silicide-polysilicon combination has better electrical properties than polysilicon alone and still does not melt in subsequent processing. Also the threshold voltage is not significantly higher than with polysilicon alone, because the silicide material is not near the channel. The process in which silicide is formed on both the gate electrode and the source and drain regions is sometimes called salicide, self-aligned silicide.

- When the transistors are extremely scaled down, it is necessary to make the gate dielectric layer very thin, around 1 nm in state-of-the-art technologies. A phenomenon observed here is the so-called poly depletion, where a depletion layer is formed in the gate polysilicon layer next to the gate dielectric when the transistor is in the inversion. To avoid this problem, a metal gate is desired. A variety of metal gates such as tantalum, tungsten, tantalum nitride, and titanium nitride are used, usually in conjunction with high-κ dielectrics. An alternative is to use fully silicided polysilicon gates, a process known as FUSI.

Present high performance CPUs use metal gate technology, together with high-κ dielectrics, a combination known as high-κ, metal gate (HKMG). The disadvantages of metal gates are overcome by a few techniques:[196]

- The threshold voltage is tuned by including a thin "work function metal" layer between the high-κ dielectric and the main metal. This layer is thin enough that the total work function of the gate is influenced by both the main metal and thin metal work functions (either due to alloying during annealing, or simply due to the incomplete screening by the thin metal). The threshold voltage thus can be tuned by the thickness of the thin metal layer.

- High-κ dielectrics are now well studied, and their defects are understood.

- HKMG processes exist that do not require the metals to experience high temperature anneals; other processes select metals that can survive the annealing step.

Insulator

As devices are made smaller, insulating layers are made thinner, often through steps of thermal oxidation or localised oxidation of silicon (LOCOS). For nano-scaled devices, at some point tunneling of carriers through the insulator from the channel to the gate electrode takes place. To reduce the resulting leakage current, the insulator can be made thinner by choosing a material with a higher dielectric constant. To see how thickness and dielectric constant are related, note that Gauss's law connects field to charge as:

with Q = charge density, κ = dielectric constant, ε0 = permittivity of empty space and E = electric field. From this law it appears the same charge can be maintained in the channel at a lower field provided κ is increased. The voltage on the gate is given by:

with VG = gate voltage, Vch = voltage at channel side of insulator, and tins = insulator thickness. This equation shows the gate voltage will not increase when the insulator thickness increases, provided κ increases to keep tins / κ = constant (see the article on high-κ dielectrics for more detail, and the section in this article on gate-oxide leakage).

The insulator in a MOSFET is a dielectric which can in any event be silicon oxide, formed by LOCOS but many other dielectric materials are employed. The generic term for the dielectric is gate dielectric since the dielectric lies directly below the gate electrode and above the channel of the MOSFET.

Junction design

The source-to-body and drain-to-body junctions are the object of much attention because of three major factors: their design affects the current–voltage (I–V) characteristics of the device, lowering output resistance, and also the speed of the device through the loading effect of the junction capacitances, and finally, the component of stand-by power dissipation due to junction leakage.

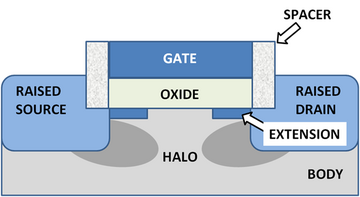

The drain induced barrier lowering of the threshold voltage and channel length modulation effects upon I-V curves are reduced by using shallow junction extensions. In addition, halo doping can be used, that is, the addition of very thin heavily doped regions of the same doping type as the body tight against the junction walls to limit the extent of depletion regions.[197]

The capacitive effects are limited by using raised source and drain geometries that make most of the contact area border thick dielectric instead of silicon.[198]

These various features of junction design are shown (with artistic license) in the figure.

Scaling

هذه section مكتوبة مثل انطباعات شخصية أو مقالة بجريدة وقد تحتاج تنظيف. من فضلك، ساعدنا على تحسينها بإعادة كتابتها بأسلوب موسوعي. (September 2016) |

| عمليات تصنيع أشباه الموصلات |

|---|

|

|

MOSFET scaling (process nodes) |

|

|

المستقبل

|

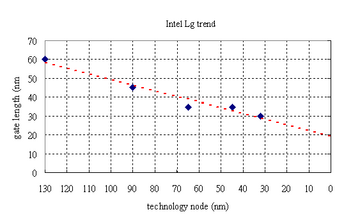

Over the past decades, the MOSFET (as used for digital logic) has continually been scaled down in size; typical MOSFET channel lengths were once several micrometres, but modern integrated circuits are incorporating MOSFETs with channel lengths of tens of nanometers. Robert Dennard's work on scaling theory was pivotal in recognising that this ongoing reduction was possible. The semiconductor industry maintains a "roadmap", the ITRS,[199] which sets the pace for MOSFET development. Historically, the difficulties with decreasing the size of the MOSFET have been associated with the semiconductor device fabrication process, the need to use very low voltages, and with poorer electrical performance necessitating circuit redesign and innovation (small MOSFETs exhibit higher leakage currents and lower output resistance). As of 2019, the smallest MOSFETs in production are 5 nm FinFET semiconductor nodes, manufactured by Samsung Electronics and TSMC.[200][201]

Smaller MOSFETs are desirable for several reasons. The main reason to make transistors smaller is to pack more and more devices in a given chip area. This results in a chip with the same functionality in a smaller area, or chips with more functionality in the same area. Since fabrication costs for a semiconductor wafer are relatively fixed, the cost per integrated circuits is mainly related to the number of chips that can be produced per wafer. Hence, smaller ICs allow more chips per wafer, reducing the price per chip. In fact, over the past 30 years the number of transistors per chip has been doubled every 2–3 years once a new technology node is introduced. For example, the number of MOSFETs in a microprocessor fabricated in a 45 nm technology can well be twice as many as in a 65 nm chip. This doubling of transistor density was first observed by Gordon Moore in 1965 and is commonly referred to as Moore's law.[202] It is also expected that smaller transistors switch faster. For example, one approach to size reduction is a scaling of the MOSFET that requires all device dimensions to reduce proportionally. The main device dimensions are the channel length, channel width, and oxide thickness. When they are scaled down by equal factors, the transistor channel resistance does not change, while gate capacitance is cut by that factor. Hence, the RC delay of the transistor scales with a similar factor. While this has been traditionally the case for the older technologies, for the state-of-the-art MOSFETs reduction of the transistor dimensions does not necessarily translate to higher chip speed because the delay due to interconnections is more significant.

Producing MOSFETs with channel lengths much smaller than a micrometre is a challenge, and the difficulties of semiconductor device fabrication are always a limiting factor in advancing integrated circuit technology. Though processes such as atomic layer deposition (ALD) have improved fabrication for small components, the small size of the MOSFET (less than a few tens of nanometers) has created operational problems:

- Higher subthreshold conduction

- As MOSFET geometries shrink, the voltage that can be applied to the gate must be reduced to maintain reliability. To maintain performance, the threshold voltage of the MOSFET has to be reduced as well. As threshold voltage is reduced, the transistor cannot be switched from complete turn-off to complete turn-on with the limited voltage swing available; the circuit design is a compromise between strong current in the on case and low current in the off case, and the application determines whether to favor one over the other. Subthreshold leakage (including subthreshold conduction, gate-oxide leakage and reverse-biased junction leakage), which was ignored in the past, now can consume upwards of half of the total power consumption of modern high-performance VLSI chips.[203][204]

- Increased gate-oxide leakage

- The gate oxide, which serves as insulator between the gate and channel, should be made as thin as possible to increase the channel conductivity and performance when the transistor is on and to reduce subthreshold leakage when the transistor is off. However, with current gate oxides with a thickness of around 1.2 nm (which in silicon is ~5 atoms thick) the quantum mechanical phenomenon of electron tunneling occurs between the gate and channel, leading to increased power consumption. Silicon dioxide has traditionally been used as the gate insulator. Silicon dioxide however has a modest dielectric constant. Increasing the dielectric constant of the gate dielectric allows a thicker layer while maintaining a high capacitance (capacitance is proportional to dielectric constant and inversely proportional to dielectric thickness). All else equal, a higher dielectric thickness reduces the quantum tunneling current through the dielectric between the gate and the channel. Insulators that have a larger dielectric constant than silicon dioxide (referred to as high-κ dielectrics), such as group IVb metal silicates e.g. hafnium and zirconium silicates and oxides are being used to reduce the gate leakage from the 45 nanometer technology node onwards. On the other hand, the barrier height of the new gate insulator is an important consideration; the difference in conduction band energy between the semiconductor and the dielectric (and the corresponding difference in valence band energy) also affects leakage current level. For the traditional gate oxide, silicon dioxide, the former barrier is approximately 8 eV. For many alternative dielectrics the value is significantly lower, tending to increase the tunneling current, somewhat negating the advantage of higher dielectric constant. The maximum gate–source voltage is determined by the strength of the electric field able to be sustained by the gate dielectric before significant leakage occurs. As the insulating dielectric is made thinner, the electric field strength within it goes up for a fixed voltage. This necessitates using lower voltages with the thinner dielectric.

- Increased junction leakage

- To make devices smaller, junction design has become more complex, leading to higher doping levels, shallower junctions, "halo" doping and so forth,[205][206] all to decrease drain-induced barrier lowering (see the section on junction design). To keep these complex junctions in place, the annealing steps formerly used to remove damage and electrically active defects must be curtailed[207] increasing junction leakage. Heavier doping is also associated with thinner depletion layers and more recombination centers that result in increased leakage current, even without lattice damage.

- Drain-induced barrier lowering (DIBL) and VT roll off

- Because of the short-channel effect, channel formation is not entirely done by the gate, but now the drain and source also affect the channel formation. As the channel length decreases, the depletion regions of the source and drain come closer together and make the threshold voltage (VT) a function of the length of the channel. This is called VT roll-off. VT also becomes function of drain to source voltage VDS. As we increase the VDS, the depletion regions increase in size, and a considerable amount of charge is depleted by the VDS. The gate voltage required to form the channel is then lowered, and thus, the VT decreases with an increase in VDS. This effect is called drain induced barrier lowering (DIBL).

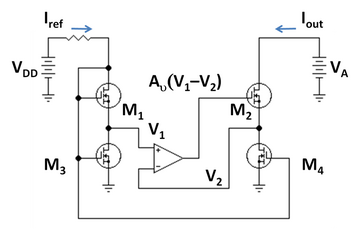

- Lower output resistance

- For analog operation, good gain requires a high MOSFET output impedance, which is to say, the MOSFET current should vary only slightly with the applied drain-to-source voltage. As devices are made smaller, the influence of the drain competes more successfully with that of the gate due to the growing proximity of these two electrodes, increasing the sensitivity of the MOSFET current to the drain voltage. To counteract the resulting decrease in output resistance, circuits are made more complex, either by requiring more devices, for example the cascode and cascade amplifiers, or by feedback circuitry using operational amplifiers, for example a circuit like that in the adjacent figure.

- Lower transconductance

- The transconductance of the MOSFET decides its gain and is proportional to hole or electron mobility (depending on device type), at least for low drain voltages. As MOSFET size is reduced, the fields in the channel increase and the dopant impurity levels increase. Both changes reduce the carrier mobility, and hence the transconductance. As channel lengths are reduced without proportional reduction in drain voltage, raising the electric field in the channel, the result is velocity saturation of the carriers, limiting the current and the transconductance.

- Interconnect capacitance

- Traditionally, switching time was roughly proportional to the gate capacitance of gates. However, with transistors becoming smaller and more transistors being placed on the chip, interconnect capacitance (the capacitance of the metal-layer connections between different parts of the chip) is becoming a large percentage of capacitance.[208][209] Signals have to travel through the interconnect, which leads to increased delay and lower performance.

- Heat production